# **Bachelor** Thesis

Julius-Maximilians-UNIVERSITÄT WÜRZBURG

# Aggregatable Remote Attestation for IoT

**Vasil Alistarov** Department of Computer Science Chair of Computer Science II (Secure Software Systems)

**Prof. Dr. Alexandra Dmitrienko** First Reviewer

**Prof. Dr. Alexandra Dmitrienko** First Advisor

**BSc. Ala Eddine Ben Yahya** Co-advisor

# Submission 27. December 2020

www.uni-wuerzburg.de

# Abstract

With the recent spike of Internet of Things (IoT) and "smart" devices, there has also been an increase in the amount of attacks on IoT networks. Wide-reaching attacks such as the one from the Mirai botnet in 2016 [1] show how crucial it is to know that a device can be trusted before initiating communication.

Remote Attestation (RA) is a proven method for asserting that a device is in a benign state. It is a challenge-response process between two parties, where the first checks the trustworthiness of the second. However, it is characterisable with low scalability – a critical issue in the IoT sector. In our work, we model a new RA protocoll, called *Aggregatable Remote Attestation*, which would allow a device to process multiple RA challenges simultaneously. We base it on the already existing SIMPLE architecture [2] and implement it as a Proof-of-Concept (PoC) by modifying the code of the Security MicroVisor (S $\mu$ V) – the core component of SIMPLE.

We evaluate our work in terms of security and performance and show that it greatly outperforms the underlying SIMPLE. We discuss the relevance of our design in relation to the IoT sphere and denote a small set of potential topics for future work and research.

# Zusammenfassung

In den vergangenen Jahren wurde ein rapider Anstieg der Anzahl der Internet of Things (IoT)-Geräte beobachtet, welcher sich auf die rasante Digitalisierung zurückführen lässt. Allerdings hat dies ein unerwünschtes Seiteneffekt mit sich gebracht: die Frequenz der Angriffe auf IoT-Netzwerke ist ebenso gestiegen und diese werden immer umfangreicher. Es ist damit klar ersichtlich, wie wichtig es ist, die Sicherheit und den vertrauenswürdigen Zustand einer IoT-Entität überprüfen beziehungsweise nachweisen zu können.

Unter den berühmtesten Mitteln zur Feststellung der Vertrauenswürdigkeit eines Geräts ist die sogenannte Remote Attestation (RA) [3] – ein Challenge-Response-Verfahren zwischen zwei Perteien, Verifier (VRF) und Prover (PRV) genannt, und den gutartigen Zustand des Letzteren zu überprüfen. Dies ist insbesondere bei kleinen IoT-Geräten relevant, die oft keine sonstigen Sicherheitsmechanismen besitzen [4]. Unglücklicherweise lässt sich die RA, als ein eins-zu-eins-Prozess, relativ schlecht skalieren, was ein enormer Nachteil im IoT-Sektor darstellt. In unserer Arbeit konzipieren wir eine sogenannte Aggregatable Remote Attestation, die es einer PRV-Entität ermöglicht, mehreren RA-Herausforderungen gleichzeitig zu verarbeiten.

Diese Aggregatable RA bauen wir auf SIMPLE [2], einem bereits existierenden RA-Protokoll, auf. Wir modifizieren dieses und implementieren unser Konzept als Proof-of-Concept (PoC) mithilfe des Quellcodes vom Security MicroVisor (S $\mu$ V), dem Kernelement von SIMPLE. Anschließend evaluieren wir unser Design bezüglich Performanz sowie Sicherheit und zeigen, dass diesen keine weiteren schwerwiegenden Sicherheitslücken im RA-Prozess schafft. Wir diskutieren über die Relevanz unseres Designs in Relation zur IoT und erörtern dazu auch einige eventuelle Themen für zukünftige Forschung.

# Contents

| 1. | Introduction                                                                                                                                                                                                                                                                                                                      | 1                                                                                                          |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 2. | Background         2.1. Establishing Trust         2.2. (Remote) Attestation                                                                                                                                                                                                                                                      | <b>3</b><br>4<br>5                                                                                         |

| 3. | Related Work         3.1. Hardware-based RA         3.2. Software-based RA         3.3. Hybrid RA         3.4. Application of Attestation         3.5. Summary                                                                                                                                                                    | <b>9</b><br>9<br>10<br>11<br>12<br>13                                                                      |

| 4. | Aggregatable Remote Attestation         4.1. Problem Statement         4.2. Approach         4.3. Architecture Evaluation and Selection         4.4. Functionality of SIMPLE         4.5. Modifications         4.6. Further Considerations         4.6.1. Retention of Dynamic Functionality         4.6.2. Formal Verifiability | <ol> <li>15</li> <li>17</li> <li>18</li> <li>20</li> <li>22</li> <li>23</li> <li>23</li> <li>24</li> </ol> |

| 5. | Implementation5.1. Microcontroller Testbench5.2. Security MicroVisor5.3. Modifying the Prover5.4. Modifying the Verifier5.5. Running the Project                                                                                                                                                                                  | <ul> <li>25</li> <li>25</li> <li>26</li> <li>27</li> <li>28</li> </ul>                                     |

| 6. | Evaluation         6.1.       Performance Evaluation         6.1.1.       Prover Performance         6.1.2.       Verifier Performance         6.1.3.       Size Comparison         6.2.       Security Evaluation         6.2.1.       Comparison to SIMPLE         6.2.2.       Other Attack Vectors                            | <b>31</b><br>31<br>33<br>34<br>34<br>34<br>34<br>35                                                        |

| 7. | Conclusion                                                                                                                                                                                                                                                                                                                        | 37                                                                                                         |

| List of | Figures |

|---------|---------|

|---------|---------|

39

| List of Tables                                                                                                                                                                                                   | 39                                                                                           |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| Listings                                                                                                                                                                                                         | 41                                                                                           |  |  |

| Acronyms                                                                                                                                                                                                         | 41<br>45<br>45<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47<br>47 |  |  |

| Bibliography                                                                                                                                                                                                     |                                                                                              |  |  |

| Appendix         A.       Adversary Knowledge after SIMPLE Modifications         B.       Custom List Implementation in C.         C.       Data Format in the Aggregatable RA         D.       Raw Testing Data | 51<br>52<br>52                                                                               |  |  |

# 1. Introduction

In the past years, a drastic increase of the amount of Internet of Things (IoT) devices has been observed. Not only has there been a spike in the total number of "smart" devices used and produced, but also many formerly analogue systems have been updated and digitalised, making them part of the IoT world. Now, its elements can be found in all spheres of our lives, reaching from the homes to as far as the medicine and the industry [5].

However, this also entices numerous malicious adversaries willing to infiltrate IoT networks, by widening their attack possibilities. Indeed, with the expansion of the IoT sector, there has also been an upsurge of attacks that have occasionally proven to be remarkably costly or to affect devices on a huge scale [1, 6, 7]. Hence, one must always strive to assert the security and benignness of any entities they communicate or interact with. This is a critical issue especially in the area of resource-constrained IoT devices, as those often do not come with any built-in security mechanisms [4]. Furthermore, classical applications and approaches are unsuitable there due to the limitations in terms of memory or computational power.

Among the best-known techniques for a (small) "smart" device to show its trustworthiness is the Remote Attestation (RA) [3]. It is an one-to-one process between a trusted and an untrusted entity, called Verifier (VRF) and Prover (PRV), respectively. RA follows a challenge-response model, with VRF sending a challenge with specific parameters, called Attestation Request (AR), such that PRV can only answer correctly if and only if it is currently in a benign state (i.e., not infected by malware) [3]. Research has already been conducted in the sphere of RA; indeed, multiple architectures have already been created, and there is vigorous ongoing research in that sphere.

Still, RA in its classical form does exhibit remarkably low scalability. That is a crucial issue in the IoT sphere, where there may be hundreds or thousands of devices communicating. A device may, for instance, need to store a large amount of symmetric keys for the attestation to work safely, or be faced with numerous ARs at once after being inactive for some period of time. To the best of our knowledge, no RA architecture exists such that it solves these issues.

#### Goals and Contribuions.

This gap is also what inspires our work. Here, we will attempt to construct a RA protocol targeting low-end devices which, unlike the classical RA, can function on an one-to-many

basis and is hence significantly more efficient. In particular, we hope to enable the PRV party to process multiple ARs at the same time, while also producing a report that is verifiable to all VRF parties. An architecture with this property will go a long way towards improving the efficiency of RA in the IoT sector, and will therefore be a crucial addition to the vast spectrum of currently existing RA techniques.

Our work will take the format of a Bachelor's thesis, thus concluding our studies of Computer Science towards the degree of Bachelor of Science (BSc.) at the Julius-Maximilians-University of Würzburg. Moreover, our work is also motivated by the Secure Internet of Things Management PLatform (SIMPL) project [8], at which the JMU is involved, among other parties. In SIMPL, trust assessment of devices can be achieved with the assistance of RA. Notably, the participating entities have access to a Blockchain (BC), for example, for logging or storing sensitive data. This allows a VRF to, e.g., query the BC in order to fetch the states of a PRV that are considered valid, and match them against the one PRV sent as a response to the attestation challenge. We aim to show that the trust management framework of SIMPL provides the flexibility to offer secure and functional one-to-many RA as a novel solution.

#### Outline.

The rest of our work is organised as follows. The next Chapter 2 concerns itself with the general security and trustworthiness in the IoT sphere; furthermore, it provides an introduction to the concept of RA, giving us a base to build upon. Chapter 3 presents an overview of a set of existing RA architectures, grouping them by types. The subsequent Chapter 4 forms the main part of our work. There, we discuss the RA process in an one-tomany scenario and show its inefficiency. We afterwards design the so-called *Aggregatable Remote Attestation* which builds on a selected one of the techniques presented in the previous Chapter 3. Thereupon, in Chapter 5, we present in detail our implementation of the Aggregatable RA as a Proof-of-Concept (PoC). In the following Chapter 6, we evaluate our design in terms of both security and performance, showing its efficiency even in the case of a large amount of RA challenges. Finally, Chapter 7 concludes our work by summarising it and also suggesting some points for future research.

# 2. Background

Ever since a modified vending machine at the Carnegie Mellon University became the first (non-computer) device to be connected to the Internet [9], the number of such appliances has been constantly on the rise. Some 17 years later, in 1999, the term IoT was proposed by the British technology pioneer Kevin Ashton as a description for a system of interconnected devices [10]. The devices-per-capita ratio would then go on to increase from 0.08 in 2003 to 1.84 in 2010 [11].

Nowadays, IoT refers to the concept of having intelligent physical objects, dubbed "Things", that autonomously share data and communicate with each other over the Internet, as well as integrating them to the global Internet infrastructure [9]. Thus, a vast information system is created. Every year, new "smart" gadgets emerge, and digital, computerised components are being added to previously analogue systems, integrating them into the IoT world. Its elements can be currently found almost everywhere, starting from our homes (heat and light sensors, printers, smart TVs) and reaching up to the medicine and the military (robotic assistants, drones) [5]. For this reason, it is no wonder that IoT has a stable and very relevant position in the business and economics of today. The online statistics portal Statista has estimated that, as of 2030, there will be over 50 billion IoT devices worldwide [12]. For the purpose of comparison, that number denotes an amount over twice as large than the one approximated for 2018.

While the very nature of IoT encourages user-defined applications, it does also mean that (in some fields more than in others) the applied security measures may be rather generic. This is supported further by the above mentioned exponential growth of IoT over such a short period of time: just a couple of years ago, probably few would have expected that a scenario of billions of interconnected devices worldwide is plausible; therefore, the security aspect might not have been considered of great relevance during design phase.

Alas, the rising amount of embedded and IoT devices, as well as their applications, also turns them to rather attractive targets and thus widens the attack possibilities of adversaries willing to infiltrate IoT networks. This is splendidly exemplified by well-known cases such as the Stuxnet worm [6] from 2010 and the Mirai botnet [1] from 2016, where the infection of critical devices has significantly endangered various systems, sometimes even on a global level. More recently, in 2018, the developer platform GitHub<sup>1</sup> suffered the largest Distributed Denial of Service (DDoS) attack in history, peaking in 1.35 Tbps [7] – way over the previous record, which was held by Mirai. One can therefore easily see how

<sup>&</sup>lt;sup>1</sup>https://github.com/

crucial it is to have reliable, proven means to establish the trustworthiness of an IoT entity before initiating any sort of communication or cooperation whatsoever.

# 2.1. Establishing Trust

Breaches in security can often be traced back to flaws of the applications or the Operational System (OS) run by the compromised device [3]. The most straightforward solution would be, without doubt, to design and write applications and OSes in such a way that they are bug-free and exploit-proof. Alas, this is barely possible in theory, let alone in practice. Modern OSes have an extremely high complexity degree even without considering the myriad of drivers and applications that exist and introduce new possible attack vectors. Consequently, any rigorous testing methods that can be found are also suboptimal in terms of complexity, but also affordability. On the other hand, cheaper and simpler solutions would probably not suffice as an assertion of a system's security. Even if the opposite were the case, yet another challenge then emerges by the users as unpredictable actors who may, through their actions, introduce security holes into a system themselves.

Therefore, it is clearly visible that no absolutely secure OS or application can exist, such that it simultaneously conforms to the modern standards regarding performance and functionalities [3]. This has forced developers and researchers aiming to create trustworthy platforms to opt for (or come up with) alternatives with wide applicability which are also plausible to implement in practice.

Among the most wide-spread methods working towards that goal in current days is the usage of Trusted Computing. That concept gained popularity with its introduction to the general public in 2005 by the Trusted Computing Group (TCG), successor of the Trusted Computing Platform Alliance, which informally defines a "trusted system" as one that "behaves in the expected manner for a particular purpose" [3]. Still, descriptions of what is called a Trusted Platform Module (TPM) can be found in works dating as far as 2001, as discussed by S. Pearson [13], and architectures like AEGIS [14] were created even earlier.

The TCG sets three major requirements to any Trusted Platform [3]:

- shielded locations and protection capabilities onto the platform that are safeguarded by means of hardware or software,

- the ability to measure (and store measurements of) the own integrity and state (that is, before all, the content of the memory), and

- mechanisms for *attestation*, i.e., asserting the benign state of the device.

Those categories, whilst listed separately, often make use of each other to fulfill their goals. Secure storage is more often than not provided onto the platform by the manufacturer, for example, in the form of (Programmable) Read-Only Memory (ROM), or PROM. Self-measurement is not difficult to achieve by simply deploying code with that functionality. In this work, we are however especially interested in the 3rd category – the attestation. In particular, we will be looking into what is known as RA. Other attestation types include attestation by the TPM, platform authentication, etc.

As for the TPMs themselves, their main tasks include (pseudo-)random number generation (such as nonces, or derived keys), data sealing (by using the protected storage), and hashing of given information (such as the contents of the device's memory) [15]. TPMs are often regarded as *roots of trust*, that is, the first piece in a device's chain of trust.

# 2.2. (Remote) Attestation

One of many definitions of RA, as given in [16], is "the activity of making a claim to a 3rd party about the properties of an entity by supplying evidence which supports that claim" – or, in other words, proving that an entity is not behaving in an unexpected, malicious way. RA inside a given network demands the existence of at least one device in a benign state, i.e., a device that is sure not to be infected by malware; such device is called a VRF. VRF *attests* an untrusted entity, called PRV, using a challenge-response principle. The challenge is modelled in such a way that PRV can generate a valid response to it if and only if it is currently not infected by malware [3]. RA is not limited to the IoT world only – while there it can be applied to assert that a device is safe and behaving as expected, one can also use it in different contexts. For instance, software developing institutions can use it to check for unauthorised changes of their product, or whether the copy of the product is genuine.

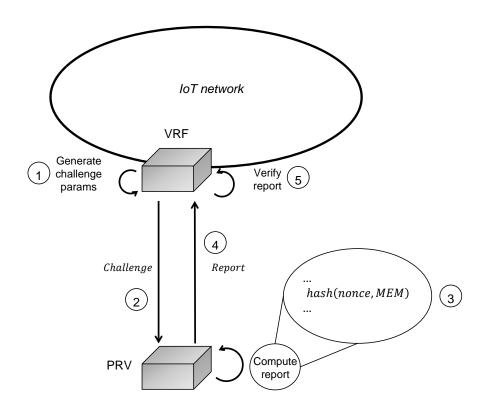

At this point we consider it important to give a more detailed overview of a standard RA process, for better understanding. For visualisation, the reader should refer to Figure 2.1. There, an example of RA depicting a use in the IoT sphere is given, where a new device may, e.g., wish to join an IoT network and needs to be attested beforehand. As mentioned earlier, that process includes two parties – VRF and PRV. Understandably, the exact implementation will vary between the different architectures; yet, the base principle will remain the same.

Figure 2.1.: Classical Remote Attestation process with a Verifier and a Prover. An example from the IoT sphere.

Often, VRF and PRV are expected to share a secret symmetric key  $K_{att}$ . In both parties, this key must be protected from unauthorised access, for example, in a memory region safeguarded by means of hardware. At some point, VRF will initiate the RA process. It

begins by generating the challenge parameters specific for that cycle (1), such as the nonce or the boundaries of the exact memory region which is to be attested. It will then send an attestation request to PRV containing those parameters (2). The parameters may be also encrypted with  $K_{att}$ . Once PRV receives them, it performs a call to the instance of the RA architecture deployed onto it (3). That architecture should, for example, compute a cryptographic hash of the memory region defined by the received boundaries using the secret key and the nonce<sup>2</sup>. Any other data required by VRF is also hashed. The resulting report is then sent back to VRF (4), who verifies its validity (5) also with the help of the key. This can be done by VRF either by computing the expected values itself, or by comparing the received report with a list of valid values<sup>3</sup>. Should the result be evaluated as valid, PRV is declared to be in a benign state and therefore trustworthy. Note once again that some architectures might have slight deviations from this description. A crucial consideration is that without the shared secret which is  $K_{att}$ , an attacker could impersonate PRV. This is possible by listening to the network, thus getting the challenge parameters, and then, e.g., computing the (now keyless) hash of the memory region and the other parameters (as an adversary is supposed to have access to all non-protected memory).

The classical RA is hence an one-to-one process as it includes only two actors. In particular, the necessity to use shared symmetrical keys between the two parties is also a significant issue, since for a single entity, the number of keys it needs to store exhibits linear growth in relation to the total number of entities in the IoT network. This also points to the low scalability of the classical RA as nowadays networks can easily contain thousands or even millions of devices.

IoT networks often include various low-end devices, such as sensors, with very limited computational and memory resources on their disposal. As an example, consider a simple light sensor in a Smart Home environment. Moreover, for such platforms, security may be an aspect that has not been given high priority by the manufacturers either, for instance, due to economic incentives [4]. These limitations are critical to consider when choosing an appropriate RA scheme.

RA can be performed through techniques that can be separated in four distinct groups – hardware-based, software-based and hybrid<sup>4</sup> – as described in [18]. The first type includes RA performed in terms of ROM, secure co-processors and additional secure hardware attached to the platform. The deployment of such hardware elements over a large network of devices, while possible, could eventually prove rather costly.

Thus, hardware-based solutions of this sort are at times rather unwell suited for utilisation in the IoT context. On the other hand, software-based RA architectures often rely on very restrictive assumptions [19], and various attacks against these have already been demonstrated [20]. An alluring alternative is created by opting to also include elements such as ROM and a Memory Management Unit (MMU) to assert the correct workflow of the attestation process, resulting in a hybrid solution. This basic idea can also be applied to lower-end devices – a property likewise valid for some hybrid architectures, i.e., ones that rely on hardware with some assistance by software. That flexibility is what motivates many other researchers as well. Indeed, research and both theoretical and practical work has already been done on the topic of designing such manageable techniques that are able to operate with minimal requirements – as presented in Chapter 3.

Finally, worth mentioning for the sake of inclusion are some RA subtypes with various properties. Note however that we do not consider them well suited for our use cases, and

<sup>&</sup>lt;sup>2</sup>Recall that hashing, along with secure storage, is one of the requirements for TPMs by the TCG.

$<sup>^{3}\</sup>mathrm{These}$  could be, e.g., directly stored inside VRF, or fetched from a database.

<sup>&</sup>lt;sup>4</sup>An alternative grouping of RA techniques, based on their exact approach, as well as an analysis of those groups' properties, is presented in [17]. Note that this grouping is out of scope for this work.

will therefore leave them, for the most part, out of the scope of this work.

- *runtime attestation* concerns itself with generating attestation evidence during runtime. Examples include the work in [21] and ATRIUM [22].

- control flow attestation can be considered a type of runtime attestation and works by asserting that an application's control flow path is correct possibly without requiring the source code. Notable mentions are C-FLAT [23] and LO-FAT [24].

- *RA with resilience to physical attacks* also exists, although most RA architectures exclude this scenario. Notable examples include DARPA [25], EAPA [26] and SCAPI [27].

# 3. Related Work

RA is a sphere of growing relevance in the IoT sector, as was previously discussed. It is, therefore, no wonder that there has been vigorous ongoing research focused on perfectionating the existing RA architectures and developing new, even more robust ones. In this section, a non-exhaustive overview of selected RA schemes for low-end IoT devices is presented, together with their requirements, main benefits and disadvantages. It is important to note that, unless mentioned otherwise, most of those techniques have been designed with the same – or very similar – adversarial model in mind, namely an adversary that has control over both the platform of PRV and the communication channels. In other words, it can freely load and unload malicious code, read unprotected memory, eavesdrop, inject packages, etc. However, it is assumed that the adversary does not (or cannot) tamper with the hardware itself, so as to, e.g., physically extract stored secrets.

# 3.1. Hardware-based RA

Hardware-based schemes are ones that modify the platform's hardware (or introduce additional pieces of hardware) to provide dynamic attestation. They utilise modules like secure co-processors, memory management units and ROM. Additional CPU instructions can optionally be introduced as well. A vast number of devices, such as laptops and even smartphones, already employ similar procedures.

#### TrustLite

One of the two architectures that build up a "base" for RA schemes on small devices is TrustLite [4]. It relies on a programmable ROM (PROM) and a Memory Protection Unit (MPU) – a lightweight version of a standard MMU. TrustLite provides its functionalities based on four main components: an execution-aware MPU (EA-MPU) that controls access based on both queried and calling code addresses, a Secure Loader setting the appropriate rights in the EA-MPU during boot, a custom Interrupt Service Routine (ISR) protecting against data leakages during interrupts, and a "trustlet" table with information about every trusted application. The authors point to the architecture's flexibility as its main benefit. They state that it can easily be modified to perform different tasks, depending on what is needed. Moreover, they mention that modifying a device engine to run TrustLite has, in their experience, proved rather easy. The main disadvantage of TrustLite remains its static initialisation: no guarantees on security can be made in case an application is deleted or a new one is added during runtime.

#### TyTAN

The above-mentioned problem is exactly what TyTAN [28] aims to solve. The TyTAN architecture, which is similar to TrustLite, allows for tasks to be loaded and unloaded during runtime while still maintaining functioning RA capabilities. Like TrustLite, it assumes that the device has an MPU and a ROM unit at its disposal. However, a real-time operational system (RTOS) is also needed to meet the real-time guarantees that the authors aim to provide. Similarly to TrustLite, TyTAN makes use of an EA-MPU and a secure boot component. A set of keys is available as well, so as to enable secure Inter-Process Communication (IPC). Another crucial element is its EA-MPU driver, which modifies the EA-MPU dynamically when a task is loaded or unloaded. Finally, instead of a custom ISR, a trusted Interrupt Multiplexer (Int Mux) is applied before calling the interrupt handler. The tasks are separated in *secure* and *normal* tasks. Even the OS has no access to the latter. The TyTAN architecture has been implemented as a PoC. While little data has been provided regarding the overall performance of TyTAN, the general understanding that the memory overhead is significant.

#### Sancus 2.0

A well-known architecture, Sancus [29], has been redesigned and improved to form Sancus 2.0 [30]. Targeted devices are resource-constrained ones similar to a MSP430. Sancus 2.0 can be used for module isolation, RA, as well as secure communication. A set of cryptographic functions and safely stored keys is used, as well as a custom Memory Access Logic circuit for program counter-based memory protection. The authors also extend the core with additional instructions, e.g., for encryption and decryption used in RA. There, the contents of the device are encrypted and sent to VRF. A nonce and various keys guarantee freshness and authenticity. The authors also provide a PoC and argue about the security of Sancus 2.0's functionalities. They show that the overhead of using Sancus 2.0 is acceptable.

# 3.2. Software-based RA

Architectures implemented entirely in code also exist. While this can be considered an advantage, they often rely on assumptions regarding, e.g., the adversary model which are rather unrealistic. Among the most common ones are "adversarial silence" during the RA process [31], as well as tight time or storage space constraints [2].

#### SWATT

This scheme [32] relies roughly on the same ideas as Pioneer [33], the first software-based RA architecture. It is designed for small devices, with the authors providing a PoC on an 8-bit microcontroller. While no dedicated hardware is required, VRF is assumed to have exact knowledge of PRV's hardware specifications. SWATT uses (pseudo-)random traversal of PRV's memory to calculate its checksum. The crucial element is that the calculation is made in such a way that even a single additional if-command injected by malware would add a noticeable time overhead. The authors point that SWATT can also be used for virus checking; however, the assumptions they set are not realistic (VRF needing to know exact hardware specifications of PRV, etc.).

#### SIMPLE

The authors of SIMPLE [2] aim to provide formally verified RA. This work forms a bridge between software-based and hybrid RA as it requires no additional hardware modules (except for, e.g., Flash memory which is considered standard. Hence our decision to place it in this Section), but makes use of a Security MicroVisor  $(S\mu V)[34]$  (software-based). It is its duty to load applications, verifying them beforehand. Unsafe applications trying to compromise the memory are denied access; unsafe, but necessary operations are replaced by virtualised safe ones stored in  $S\mu V$ 's memory. RA is achieved by hashing the memory and makes use of an authentication and an attestation key shared between VRF and PRV. The authors argue formally that SIMPLE is secure if  $S\mu V$  is the first application to be loaded.

## 3.3. Hybrid RA

Those RA schemes that rely on a combination of software and hardware security features are also known as *hybrid* ones. In particular, they relax the unrealistic assumptions associated with software-based approaches by also allowing hardware modifications or additional hardware elements. Hybrid schemes are proven to be applicable on low-end devices as well, making them attractive for this work.

#### SMART

Together with TrustLite, SMART [31] builds up the base of many hardware-based and hybrid RA schemes. The prerequisites for SMART most notably include a shared secret key K between VRF and PRV, a so-called "Attestation ROM", and a secure storage inside the CPU accessible only from SMART code. Two compiler enhancement tools, Deputy and CQUAL, are applied in the SMART procedure to tackle possible memory leakages. The authors argue that, based on their PoC, the only possibly relevant overhead is the calculation of the checksum. The main benefit of SMART is that it is not only easily implemented, but also multi-functional due to the optionally executed code. This allows it to be used for, e.g., attested measurement reading. Dynamic application (un-)loading is not considered.

#### **SMARM**

The authors of SMARM [35] aim to solve the problem represented by *roving malware*, that is, malware that can relocate itself. Their work is heavily based on SMART and has the same requirements, with the addition of a reliable read-only clock. SMARM works by attesting PRV's memory segment-wise using SMART, with events such as adversary allocation and device functionalities being allowed to occur only in between two block attestations. The measurement order is a random permutation defined at the beginning and kept inside a protected storage. Since SMARM is non-deterministic, its malware detection rate is not 100% as shown by the authors. It is however possible, by repeating the process multiple times, to reduce the failure probability. SMARM's biggest strength is allowing the device to function during RA time. However, this also represents a weakness as it allows the adversary to avoid detection by roaming through the memory during the RA process.

#### HYDRA

This is a relatively new hybrid RA technique [18] that does not explicitly require any MPU or ROM; however, it makes use of the separate microkernel seL4 [36] as its only prerequisite. Note that seL4 itself does require some minor hardware modifications of the microcontroller it is deployed on. HYDRA borrows some key elements from SMART such as attesting the content inside some boundaries given by VRF. It does not, however, offer code execution at a given address, or secure inter-process-communication. Thus, its general functionality consists of verifying the validity of the RA request to avoid possible

Denial of Service (DoS) attacks, and then computing a cryptographic checksum of the code segment in the given boundaries. For access control, ROM and secure storage, HYDRA relies on seL4. The seL4 microkernel is also the main drawback of HYDRA: while it does remove the need for ROM and MPU, these are very often available in embedded devices by default. Thus, seL4 represents an additional piece of software which is not needed for other purposes. Moreover, the authors of HYDRA explicitly state that their architecture does not aim at really small devices, but at rather more sophisticated ones. The main benefit is that only little modifications are required on the original device platform.

#### HEALED

HEALED [37] is novel in that it provides not only attestation but also recovery of infected devices to benign state. Required are only a ROM and a MPU. HEALED functions by making a random device try to attest another one at a random interval. PRV's memory is divided into ordered segments and attested by hashing in a tree-like manner, creating a Merkle Hash Tree. If PRV turns out to be infected, VRF seeks a third device H from the same type as PRV. After successful attestation by PRV, H finds the corrupted code inside VRF by using the Merkle Tree and tries to patch it. HEALED suffers from major drawbacks in the sphere of scalability, as an exponentially rising number of devices need to share symmetric keys. On the other hand, healing is a crucial benefit that is currently rarely considered in RA schemes and thus should not be ignored. The authors provide PoC implementations over SMART, TrustLite and a drone testbench, and show that HEALED weakens the performance in a negligible range.

#### VRASED

The next hybrid RA scheme discussed here is VRASED [38], an architecture with security "verifiable-by-design". Hardware requirements are minimal: VRASED focuses on low-end IoT devices with ROM, SRAM, a Flash, and an additional small hardware module. In VRASED, the platform is divided into smaller components. They are then represented as Finite State Machines in (i) Verilog HDL, and (ii) the model-checking language SMV. The functionalities and the properties themselves are then formulated as Linear Temporal Logic formulae, and each sub-module is checked against the formulae subset it is supposed to cover. Once the sub-modules are verified, the same is done for the whole platform. While the formal verifiability is an obvious benefit, it also significantly increases the process' complexity. The authors provide an implementation on a Basys3 Artix-7FPGA board and suggest that it is portable to other platforms with minimal modifications.

#### APEX and PURE

To conclude the hybrid schemes, we mention APEX [39] and PURE [40], two architectures relying heavily on VRASED. Aside from RA, APEX is capable of generating formally provable evidence that specific code has been executed, as well as a proof that the produced result is as intended. The authors also provide an implementation on an OpenMSP430. While the memory overhead is negligible in comparison with VRASED, the additional computation time is considerable. PURE on the other hand allows for (also formally provable) system-wide reset, software update and memory erasure. Its overhead in both computation and memory is insignificant, as asserted by the authors. An implementation is also available.

## **3.4.** Application of Attestation

Here, we present approaches which are still relevant to the RA topic, but cannot be categorised as completely new or different RA primitives. They are rather novel ways to utilise already existing RA protocols.

#### ERASMUS

The ERASMUS architecture [41] belongs in a separate category since its authors do not present a completely new attestation scheme. Instead, what they contribute with is the use case. In particular, they review the case where malware can infect and leave the device between the attestation requests. This scenario is addressed by making the device self-attest at regular intervals, and save all measurements until a request from VRF arrives. Then, all saved measured states are sent and removed from the memory. While this scheme has no particular hardware requirements by itself, it demands that another attestation technique is deployed over the device (and thus inherits that technique's own requirements). The authors suggest implementations over a SMART+ and a HYDRA instance. The logs need not be stored in secure memory, as any changes inflicted by malware can be detected by VRF upon log collection. One benefit of ERASMUS, other than having a self-measurement log, is the fact that attestation requests by VRF cause no further drains of computational power than those needed to simply send all saved measurements. Furthermore, ERASMUS can be extended to provide on-demand attestation or self-attestation at irregular intervals.

#### SARA

We consider the SARA protocol [42] to be worthy of a mention, even though it is not an actual RA architecture. This work concerns itself with asynchronous RA. VRF and PRV use a synchronised vector clock which is updated after each event. SARA operates based on a publish-subscribe approach. VRF sends RA challenges to the Publisher, and the Subscriber (PRV) eventually uses them to attest itself. Once VRF sends a RA request to PRV, the Subscriber service will send the RA result. It is also possible for VRF to subscribe to the Publisher to directly receive updates about PRV. The authors demonstrate the efficiency of SARA through a PoC. They also note that the main benefits are asynchrony, selective attestation and historical evidence.

## 3.5. Summary

A large array of RA architectures and approaches tailored for resource-constrained devices already exists, and more will eventually be developed and presented in the near future. Here, we discussed a selected subset of those architectures. Some of them also offer additional features aside from RA, as we will elaborate in more details in Section 4.3. However, those are all in their essence variants of the classical RA presented in Section 2.2. Hence they inherit most of the properties typical for RA.

An exemplary issue which is not addressed is the one-to-one property observable in RA. All architectures we considered, regardless whether hardware-based, software-based, or hybrid, work with it as a base and do not attempt to improve it; however, as we will discuss in the next Chapter 4, this leads to performance issues when a PRV entity is faced with many ARs and also paves the way for some attack vectors.

Important to note here is that the SARA protocol does make progress in a similar, albeit not the same direction, by introducing the Publish-Subscribe approach. In particular, SARA does not consider the use case where there are multiple ARs coming from different VRF entities. Moreover, it still intends for PRV to process those ARs sequentially, thus not solving the performance issue. This problem will also be what our work revolves around.

# 4. Aggregatable Remote Attestation

One of the most crucial details about the classical RA is the observation of it being an one-to-one process between a Verifier VRF and a Prover PRV entity. Namely, VRF would send a challenge, also known as AR, that contains specific parameters to PRV. PRV would then be able to calculate an answer to this challenge *if and only if* it is not infected by malware. As a consequence of its one-to-one property, this process was shown to be characterisable as one with very low scalability – a crucial detail in the IoT sphere, where a single network can easily consist of well over a million smart devices. In this Chapter, we will inspect the scalability issue a bit more closely, and attempt to craft a solution by creating the so-called Aggregatable Remote Attestation.

# 4.1. Problem Statement

One could argue that the one-to-one property is not a real issue. After all, PRV just accepts the challenge parameters, executes the attestation process, and returns the report. However, in reality this is not that simple. The one-to-one approach can, for instance, easily be misused by adversaries to create a DoS scenario by bombarding PRV with ARs since PRV will be doing nothing but computing attestations. Moreover, the number of symmetric keys that need to be stored grows with the size of the network and can thus easily cause memory issues.

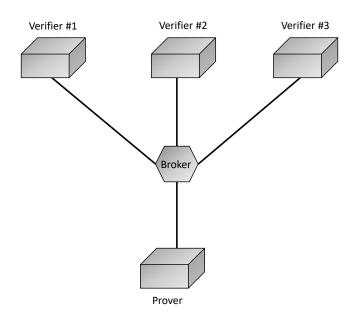

The whole problem starts to get clearer once one considers the circumstances and events surrounding the attestation. The first crucial point is that a lower-class device is often not reachable directly. An (IoT) network can be visualised as a complex graph, with the nodes representing the separate devices and the edges being the simple (i.e., with hop count = 1) connections between them. Depending on the exact architecture, a set of nodes could, for example, need to pass their whole communication with the outside world through some higher-class mediator device – a hub, a switch, or some kind of broker. A broker in this case is essentially a server that accepts messages from the above mentioned set of nodes and forwards them to their destinations, or alternatively forwards messages to the set of nodes. The underlying reason for this network design choice may vary: different possibilities include reduced coupling within the sub-network, communication control, protection against diverse attacks, etc. Regardless of the case, especially lower-end entities (the ones we are interested in) such as sensors are often "hidden" behind such a broker (cf. Figure 4.1). This implies that any ARs sent to them are first accumulated at the broker before being passed to the device.

Figure 4.1.: An IoT network including multiple devices, a broker, as well as a distinguished Prover.

Second, it is important to note that devices, regardless of their type, are not constantly available. There are (not necessarily on a regular, foreseeable base) events like maintenance, software/hardware updates, but also, for example, spontaneous downtimes during which the entity is not reachable by external traffic. Ultimately, the device might be merely "sleeping" or executing its standard tasks and due to this reason not be available for any other purposes. It is hence not completely unlikely that an incoming AR (or some other request, in that context) is not processed immediately. To tackle the issue represented by this, such messages are often accumulated at the previously mentioned broker entity. It would then wait for the device to "wake up" (or become available again) in order to send the whole list of pending messages and requests.

It can thus be clearly seen that the scenario of a device receiving multiple AR at once is not only possible, but also plausible. Naturally, more reasons exist for this aside from the broker simply collecting a set of requests. Even if we were to remove the broker entirely, it is not unfeasible that multiple entities, each acting separately as a VRF, decide to perform a RA onto the target device – maybe even simultaneously. Furthermore, a single VRF entity may due to various reasons send a second AR to the same PRV before the first has been processed. To exemplify why this can happen, examine the case where that very VRF is acting as a gateway for a larger subsystem<sup>1</sup>. With different entities from the subsystem needing to verify the trustworthiness of PRV, the gateway entity may send separate ARs. Alternatively, a subsequent AR might be triggered by some unexpected event, while the first one is part of a routine. Whatever the case, it is safe to assume that the different ARs carry different challenge parameters, and therefore need to be processed separately.

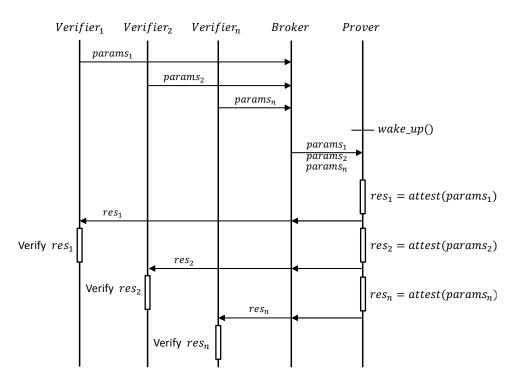

What exactly does happen inside PRV when multiple different challenges arrive? To the best of our knowledge, the currently existing RA architectures simply proceed to process those challenges sequentially. The separate ARs may also be checked for validity beforehand, but that is irrelevant for our considerations. In summary, the process goes as follows:

1. PRV wakes up/becomes reachable.

<sup>&</sup>lt;sup>1</sup>See the *Facade* Structural Design Pattern described by the Gang of Four [43].

- 2. The broker entity sends all ARs to PRV.

- 3. While there is an AR in the queue:

- 3.a) PRV attests itself with this AR

- 3.b) PRV sends report to VRF through Broker

- 3.c) Return to 3.

- 4. The results are sent back to the broker, who forwards them to the VRFs.

For visualisation, one can also refer to the sequence diagram on Figure 4.2.

An important element to note would be the repetition of the hashing of the own memory during 3.a) (as a remark, we have opted for this description since many RA architectures, as seen in Chapter 3, do indeed revolve around memory hashing). This is also the most problematic point: however small the memory size inside a low-end device might be, computing a hash over the whole memory still does take a significant amount of time and computational resources (at least in comparison to the other tasks). The addition of the nonce to the hash can be ignored in the efficiency considerations as all nonces share the same constant size and are significantly smaller than the memory. Regardless, the computation-intensive chaining of hashes could eventually result in longer periods of time where the device is bound to the attestation process and cannot proceed with its default tasks. Hence arises the opening for the DoS attack mentioned above.

Figure 4.2.: Remote Attestation process with multiple Verifiers, a Broker and a Prover.

#### 4.2. Approach

We do believe that this process can indeed be optimised.

For the optimisation, it is only logical to target the underlying reason of the problem, namely the one-to-one property. An upgrade to an one-to-many attestation process would be most advantageous and go a long way towards making RA far better suited for the IoT sphere. For instance, if PRV was able to somehow aggregate all of the pending ARs, it would then merely need to calculate a solution to the challenge aggregate and send it back to the Verifiers.

This is also the goal we aim for: A RA protocol with the capabilities to (i) aggregate challenge parameters to a single one, and (ii) produce a publicly verifiable report. In other words, the mere contents of the report should suffice as an assertion of PRV's benign state, particularly without needing any shared secrets or other non-public elements of that manner.

With meticulous considerations, a modified version of the standard RA process, as described in Chapter 2, has to be crafted. This new technique, called *Aggregatable Remote Attestation*, should allow a PRV to collect a set of ARs, iterate over them and create a single challenge, whose parameters are derived from the ones of the individual requests. PRV will then be able to compute a sole response to the challenge aggregate and return that report to the broker entities (or the Verifiers, depending on the case). Great care is to be exercised though, as that construct needs to have the property of being verifiable especially by each and every single one of the Verifiers which sent the initial ARs. This in turn entails high probability that not only the self-measurement of the PRV will need to be modified, but the verification process done by the VRF as well.

In the previous Chapter 3, we offered an overview of a selected set of RA architectures, grouped by their type: hardware-based, software-based, and hybrid. Each scheme was briefly analysed in terms of prerequisites, main benefits and disadvantages, as well as functionality. We saw that many of those schemes do indeed also offer other features aside from RA – healing of infected devices, protection against roving malware, etc.

The first part of our contribution will thus consist of the post-processing of this overview. We are to evaluate the properties of the presented schemes in accordance with our use case and present an aggregated list. Thenceforth we shall select a single architecture which we deem to be best suited as a base for the Aggregatable RA. That is, in the main part of our work we will modify the VRF and PRV algorithm of the architecture in order to convert it to an one-to-many process. In this sense, our approach bears some similarities to ERASMUS and SARA that were discussed earlier in Section 3.4, as they too employ another RA protocol at their core.

Afterwards, having picked a basis scheme, we will describe the exact modifications and how they help us achieve our goal. We argue that those changes do not introduce almost any additional security holes and attack vectors that were not present before. The only exception is that we discard the symmetric key and hence the authentication of VRF. Finally, we will discuss eventual topics for future work which, if implemented, would make the whole construct more robust.

# 4.3. Architecture Evaluation and Selection

Providing RA capabilities is what unites all techniques discussed in Chapter 3. Many of them do, however, also go beyond that and offer additional functionalities and benefits. As a first step, we are going to present those (at least as far as they are mentioned by the authors of the corresponding works):

#### **Dynamic applications:**

This denotes the capability of an architecture being able to guarantee functioning RA even if applications are loaded or unloaded during run-time. TyTAN [28] is a primary example, and SIMPLE [2] allows additionally for verification of the application safety prior to loading.

#### Asynchronous RA:

This means that the attestation is allowed to happen not immediately after the device receives the AR, but also afterwards when it is available. Notable implementor is SARA [42] which utilises a publish-subscribe approach.

#### **Code execution:**

After the self-measurement of the memory is complete, the device executes the code stored at an address passed with the challenge parameters and hashes the result. This is one of the most valuable properties of SMART [31], but is also available in APEX [39].

#### **Protection against roving malware:**

Roving malware is one that can re-allocate itself to another memory location and thus eventually avoid standard RA approaches. Pseudo-randomness-based protection is offered by SMARM [35].

#### **Recovery:**

If a device is found to be infected, performing a clean-up procedure is recommended. The only architecture offering this out-of-the-box is HEALED [37]. A relaxed property – applying memory erasure and system-wide reset – is also available in PURE [40].

#### Formal verifiability:

Many authors argue about the security of their architectures. Few do however prove it *formally*. The most notable schemes with this property are SIMPLE [2], VRASED [38] and PURE [40].

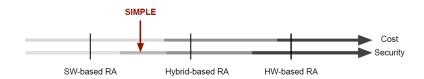

Our scheme of choice, after some considerations, is ultimately SIMPLE. While it is a really novel technique, it does indeed already appear very promising. We will now present briefly our line of thought that led to this decision.

As already noted, SIMPLE, in the form in which it was presented, can be verified formally by various means described by the authors. This provides a stable basis for extensions such as the ones we wish to apply. It does also not require any additional hardware to deploy – as the authors show, SIMPLE takes a very specific spot bridging the software-based and the hybrid architectures (cf. Figure 4.3).

Figure 4.3.: Position of SIMPLE on the spectrum of RA architectures [2].

Another positive aspect is that SIMPLE targets resource-restricted devices, exactly as the ones we are considering. Moreover, as remarked above, it operates correctly even in the case of applications being removed or new ones being loaded during run-time. As a concluding point, the authors have implemented it as a PoC to show its real-world applicability. Its main component,  $S\mu V$ , is open-source on GitHub<sup>2</sup> and can therefore be downloaded and extended freely.

$<sup>^{2}\</sup>mathrm{An}\ \mathrm{implementation}\ \mathrm{in}\ \mathrm{C}\ \mathrm{can}\ \mathrm{be}\ \mathrm{found}\ \mathrm{on}\ \mathrm{GitHub}\ \mathrm{under}\ \mathrm{https://github.com/m3mmar/verified\_SuV/.$

# 4.4. Functionality of SIMPLE

We will adapt SIMPLE to our use case and make the necessary modifications to convert it to an one-to-many architecture. However, first we will go into more details regarding SIMPLE to provide better insights about its functionalities, as we consider having understanding of its internals important for the rest of this work.

As discussed, SIMPLE falls under the software-based category as it completely relies on the Security MicroVisor  $S\mu V$ . It provides the same security guarantees as hybrid-based approaches, without requiring neither hardware support in the form of a ROM or a MPU, nor hardware modifications. Moreover, SIMPLE implicitly guarantees Control Flow Integrity, as asserted by the authors.

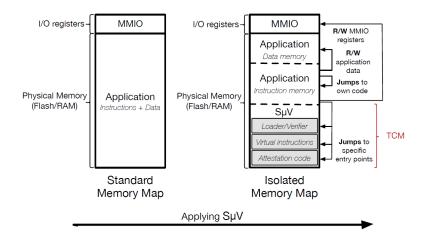

The MicroVisor  $S\mu V$  is an open-source software-based hypervisor. It provides trusted MPU-like memory protection and isolation.  $S\mu V$  uses selective software virtualisation as well as code verification on assembly level to isolate a software-based Trusted Computing Module, or TCM (similar to a TPM). A necessary and sufficient prerequisite for  $S\mu V$  is having a simple, single-threaded microcontroller that lacks an MPU, supports global interrupt disabling, and has sufficient non-volatile memory (e.g., Flash or ROM). This is standard even in small IoT devices [44] and is thus not considered an explicit hardware requirement.

$S\mu V$  needs to be installed on the device before any other application. It reserves a part of the memory for the TCM, which is immutable and has non-restricted access. The rest is split to Data Memory and Instruction Memory (cf. Figure 4.4). In particular, Data Memory is not allowed to read, write, or execute any instructions; it merely holds application data. Contrary to that, Instruction Memory can read and write data, jump freely within itself and call specific entry points of TCM memory.

Figure 4.4.: Memory mapping without and with the Security MicroVisor [2].

Figure 4.5 illustrates the memory access rules described above. Most notably,  $S\mu V$  has unrestricted capabilities within the whole program memory. On the other hand, any untrusted applications are allowed to use specific access points in the secure memory, and freely execute instructions in the non-secure program memory.

Application deployment may only occur through  $S\mu V$ , which verifies incoming applications at load time. A crucial element is that unsafe instructions, which are still essential for normal operation, are replaced by safe virtualised instructions stored in the TCM memory. Applications attempting to compromise the memory are rejected by  $S\mu V$  at boot time.

| MMIO |

|------|

|      |

|      |

|      |

\*Execution is only available from specific entry points

Figure 4.5.: Memory access rules set by the Security MicroVisor [2].

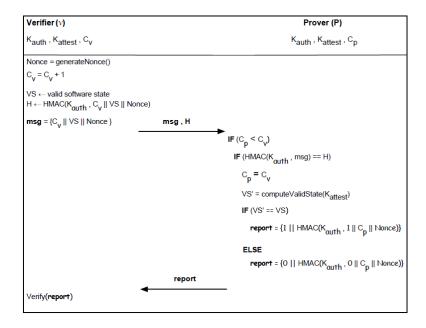

RA with SIMPLE functions as follows. At the beginning, PRV and VRF need to share two keys,  $K_{auth}$  and  $K_{attest}$ . Moreover, they have monotonically updateable counters  $C_v$ and  $C_p$ . The counters and the keys are safely stored inside the TCM memory. First, VRF increments its clock and uses  $K_{attest}$  to calculate the expected state VC of PRV. That state is sent to PRV along with the clock and a nonce, as well as an HMAC digest with  $K_{auth}$  of those elements for authentication. PRV uses the digest to verify the message and updates its own clock accordingly. Afterwards, PRV computes the digest of its current state and compares it with the expected one received from VRF to a 1/0 result. Then, for authentication, it generates the HMAC digest of that result along with the own clock  $C_p$  and the nonce, and sends the digest together with the 1/0 result back to VRF. VRF checks the authenticity of the result by using the digest, and makes a conclusion regarding PRV's benignness from that result.

The nonce and the counter are needed as a protection against replay attacks. For visualisation the reader may also refer to the scheme on Figure 4.6.

Figure 4.6.: Remote Attestation with SIMPLE [2].

For the hash function, a keyed HMAC-SHA1 is used. Security of the architecture and the algorithm is asserted as follows:

- $S\mu V$  erases all data that was temporarily stored during RA .

- At the very beginning of the algorithm, all interrupts are disabled.

- Thus, the algorithm is executed atomically. This is a protection against leakages, return-oriented programming and roving malware.

- The algorithm always finishes in finite time, as verified through model checking.

- $S\mu V$  code is immutable, therefore the results are always reliable.

That proves that if the IoT device is initialised with the installation of  $S\mu V$ , then SIMPLE is secure and guaranteed to provide secure and correct RA.

## 4.5. Modifications

As elaborated in Section 4.2, we conduct a set of adjustments to the original SIMPLE architecture. In particular, we carefully analyse the individual issues that emerge from the way it was designed initially, and take action to adjust each of them while also attempting not to deviate from the archetype more than is necessary.

For our model, we will be assuming the same adversary characteristics as the authors of SIMPLE – an attacker able to eavesdrop, inject packages, and modify *unprotected* areas of PRV's memory, but not to physically tamper with the device so as to, e.g., gain access to protected memory. Moreover, the adversary has enough computational power to attempt, for example, collision attacks. As mentioned in Chapter 3, this model is typical in the RA sphere; hence, using it sets our approach on the same level as the majority of other schemes.

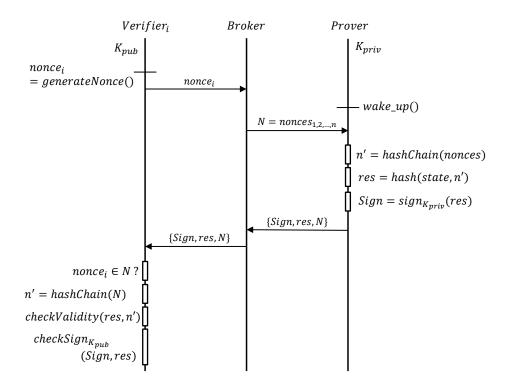

The first problem, which was in fact already briefly addressed, is related to performance: if the whole attestation is executed once for every VRF and with every nonce, this would take significant time and also creates an opening for a potential DoS attack. Therefore, once the RA process begins, we collect the important data – the nonces  $n_i$  – from all pending ARs and construct a single one by combining them, e.g., to a hash chain. Afterwards, the device proceeds to perform the rest of the RA with the new, aggregated nonce n'. In particular, n' is also hashed together with the current state (memory) to a digest we denote as *res*. When sending the result back to every VRF (or simply to the broker entity), we also append the whole list of nonces N collected from the individual ARs. This way, VRF can

- 1. check that its own nonce (or all of them, if VRF has sent multiple ARs) is included in the list, and

- 2. compute the hash chain himself.

VRF will then use the self-computed chain to verify the received result. It can, for instance, compare it with a list of valid states stored in a database or, in the case of SIMPL, a BC. One could try to argue that sending this additional data over the communication channel represents a new security threat. However, this is indeed not a vulnerability since an eavesdropping adversary could have learned the single nonces by the time they were received by PRV.

Secondly, we wish to break away from the one-to-one property of standard RA whilst still making the result verifiable for all VRF entities. An important issue here is the number of symmetric keys that PRV, a resource-constrained IoT device, has to hold in a large network. In order not to require secure key exchange beforehand (or storing symmetric keys), we replace the keyed HMAC function, currently used to hash the memory, with a keyless hashing function, such as a simple SHA-1. We argue in Section 6.2 that this does not create a new attack vector. Additionally, we opt for asymmetric cryptography and applying a digital signature on the result after computing it. For this, PRV will use a single private key  $K_{priv}$  stored in protected memory. Once the current state state is collected, PRV signs it with  $K_{sign}$  to a result Sign. It then sends  $\{Sign ||res||N\}$ . Any entities having access to PRV's public key and a list of valid states for the device can verify

that the result is correct. Any VRF who has sent a RA request can thus also verify the validity of the result and the new nonce as described above.

Finally, VRF sending a valid software state VS (even encrypted) to PRV is unnecessary. Instead of PRV, VRF will be the one checking whether PRV's state is benign or not. While it is still possible for PRV to compare its own to the expected state and return a signature of a 1/0 result together with the nonce, this is rather impractical. The rationale behind this is that eventually there can be a vast amount of benign states, and saving and comparing them inside PRV would be rather unfeasible.

For a visualisation of the modifications, we point to the sequence diagram on Figure 4.7.

Figure 4.7.: Modified version of SIMPLE.

## 4.6. Further Considerations

We conclude this chapter by briefly presenting some additional points regarding the modified RA architecture. Note that considerations regarding the security and the eventual attack vectors can be found in Section 6.2.

#### 4.6.1. Retention of Dynamic Functionality

A point which was not examined thoroughly was the property of SIMPLE allowing for valid RA in a dynamic environment, i.e., when applications are loaded and/or unloaded during run-time. The authors of SIMPLE argue that their implementation allows this [2]. Albeit our modifications do not concern themselves with the processing of the memory (or, more accurately: the exact memory locations which are processed), this use case has still not been tested appropriately. Hence, no guarantees are provided for the proper functionality of the modified RA, should applications be (un-) loaded after boot. This remains a subject of potential works in the future.

# 4.6.2. Formal Verifiability

The final sphere of discussion remains the capability of SIMPLE's RA to be verified formally in terms of functionality and security. This is a similar aspect to the one exhibited by VRASED [38], APEX [39] and PURE [40]. It is also one of the main focal points of the original SIMPLE architecture. Not unlike the dynamic environment, it is not impossible that our changes to the archetype SIMPLE have rendered the means of formal verifiability no longer usable. Again, this is a case that has not been inspected as part of our work. We estimate this aspect to be one of high complexity and far above the reach of a Bachelor's Thesis. Consequently, it can also be considered a niche for future work and research.

# 5. Implementation

To demonstrate the applicability of our design given in the previous Chapter 4, we also write an implementation as a PoC. The implementation is based on SIMPLE's core component, the Security MicroVisor  $S\mu V$ , as we derived our model of the so-called Aggregatable RA from SIMPLE. Previously, we discussed the various benefits of different architectures aside from RA, and declared SIMPLE [2] as one most suited for modifications.

# 5.1. Microcontroller Testbench

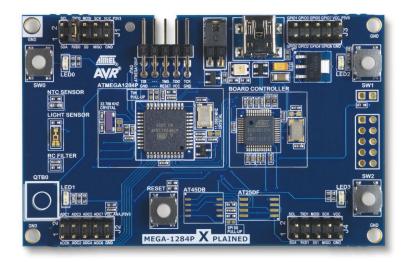

Since our work is concentrated on small devices, an appropriate one needs to be selected for the implementation. Our choice lies ultimately with the Atmel MEGA-1284P Xplained<sup>1</sup> (ATmega1284P-XPLD). The underlying ATmega1284P is a low-power 8-bit microcontroller based on the AVR enhanced RISC architecture [45]. It features 128K bytes of programmable flash memory allowing for concurrent read- and write-operations. Moreover, at its disposal are 32 general-purpose working registers, 4K bytes EEPROM, 16K bytes SRAM, as well as I/O capabilities through a SPI serial port and a JTAG test interface. A close-up view of the board is shown on Figure 5.1.

Those properties allow the ATmega1284P-XPLD to be classified as a low-end device. More accurately, it belongs to the Class 1 devices, following the definitions given by Bormann et al. [44]. This is particularly convenient for our use case as the Class 1 devices do not offer any security mechanisms out-of-the-box. Hence, showing that our Aggregatable RA can be deployed on such a device will be an important statement in regard to its applicability and usefulness.

# 5.2. Security MicroVisor

Recall that one of our arguments behind the choice of SIMPLE as the scheme to be extended did consist of SIMPLE's main underlying component, the Security MicroVisor S $\mu$ V, being available open-source on GitHub as mentioned in Section 4.3. The MicroVisor code is written in the C programming language and targets AVR architectures specifically, as described on the GitHub page<sup>2</sup> – another reason supporting our choice of the ATmega1284P-XPLD microcontroller.

$<sup>^{1}</sup> https://www.microchip.com/DevelopmentTools/ProductDetails/ATMEGA1284P-XPLD$

<sup>&</sup>lt;sup>2</sup>Once again, the repository is available at https://github.com/m3mmar/verified\_SuV/.

Figure 5.1.: The ATmega1284P-XPLD.

The code of the MicroVisor already includes RA capabilities for PRV as well as a simple VRF entity written in Python. VRF creates and sends a single nonce. Afterwards, PRV computes the already discussed hash of the memory and the nonce, implemented through a HMAC-SHA1. The exact HMAC implementation, after some research, appears to originate from the AVR-Crypto-Lib<sup>3</sup>. Finally, the result is sent back to VRF. VRF has computed a digest itself, and compares it with the one received from PRV. The communication is conducted through a serial port. The VRF code, runnable on any device that supports Python, accesses the serial port by using the pySerial library<sup>4</sup>.

# 5.3. Modifying the Prover

The first element we need to change is the nonce reading. Since we are collecting an unknown number of nonces instead of a single one, we need a flexible way to store them. Currently, the single nonce is written to a uint8\_t array of length 20. Instead, we model a double-linked list, defined as given on Listing 5.1<sup>5</sup>. Each element of the list contains pointers to the previous and the next element of the list (or NULL if no such exists) as well as a pointer to the actual nonce (again, stored as a uint8\_t array). The full header of the list can be found in Appendix B. In the RA code of  $S\mu V$ , we create a list instance and append an element for each nonce received over the serial port.

```

1 typedef struct node {

2     uint8_t * val;

3     struct node * next;

4     struct node * prev;

5     } node_t;

```

Listing 5.1: Definition of the custom list data structure.

Having saved all nonces, the next step would be to aggregate them. For this, as mentioned in Section 4.5, we can, for example, compute a hash chain (or use any other compression

<sup>&</sup>lt;sup>3</sup>Can be found at https://wiki.das-labor.org/. Link to a repository with the functions is also included.

<sup>&</sup>lt;sup>4</sup>See documentation at https://pyserial.readthedocs.io/.

<sup>&</sup>lt;sup>5</sup>For the list, inspiration was taken from https://www.learn-c.org/.

function). A simple solution is offered by the AVR-SHA1 library<sup>6</sup>, whose code we put in the core/crypto directory in the place of S $\mu$ V's HMAC-SHA1. So we define a function

1 | void aggregate\_nonces(sha1\_ctx\_t \*ctx, void \*src, void \*dest)

that accepts pointers to a SHA-1 context (ctx), the list with nonces (src), as well as a destination (dest). The function iterates through the list, feeding the single nonces to the context in a chain-like manner, and subsequently writes the digest in the dest parameter. At the end, dest contains a single 20 bytes long nonce aggregate, or n' as per Section 4.5 notation. Afterwards, the (already exiting) procedure remote\_attestation(buf) is called with the aggregate.

Next, we move on to the main MicroVisor code, stored in core/microvisor.c, and more precisely to the remote\_attestation(uint8\_t \*n) function. There, a HMAC-SHA1 context is created and initialised with  $K_{attest}$ . Afterwards, the device memory, block by block, is fed to the context, effectively computing the HMAC. Once again, we replace the HMAC-SHA1 context with a simple SHA-1 one. Note that utilising a collision-safe one-way cryptographic hash function is not entirely necessary, as we will show in Section 6.2 and the referenced Appendix A. The SHA-1 digest is placed in the buffer previously containing the nonce aggregate, in order to return it to main.c. With these changes, we have effectively implemented  $\frac{2}{3}$  of our modifications. The only remaining element (on the PRV part) is the digital signature.

Due to the relation of our work to the SIMPL project [8], as mentioned in Section 1, the signature process we opt for needs to be compatible with the one on SIMPL's BC. There, this operation is performed by using an Elliptic Curve Digital Signature Algorithm (ECDSA). The curve of choice for the algorithm is the same one as on the Bitcoin network, namely secp256k1 [46]. Hence, in order to reach compatibility, we must apply signature with the same curve.

A C library with the required capabilities is, for instance, micro-ecc<sup>7</sup>. The authors assert that it is deliberately designed to be small and fast, and so as to be applicable for 8-bit processors. We thus include the library's functional files in core/crypto. Since the ECDSA algorithm needs a source of randomness, we also add a lightweight Pseudo-Random Number Generator (PRNG)<sup>8</sup>. We use the micro-ecc library to generate a key pair. The private key is placed in secure memory, namely in the same field which used to store the key for the HMAC function. We also save the public key inside VRF. In the body of PRV's remote\_attestation(uint8\_t \*n) function, we create a signature context and sign the hash of the memory and the nonce. To return the signature digest to the main function, we add a second uint8\_t \*sign parameter and pass a uint8\_t sign[64] to it.

From there, we simply send the list of nonces, as well as the digest and then the signature, over the serial port. We utilise special characters for separating the three elements and also for denoting the end of the message. For exact description of the data format, the reader may refer to Appendix C.

# 5.4. Modifying the Verifier

In the previous section, we described our changes to the  $S\mu V$  code. However, recall that changes to the VRF side also need to be made for it to properly process the new RA results.

<sup>&</sup>lt;sup>6</sup>Available at https://github.com/.

<sup>&</sup>lt;sup>7</sup>Available at https://libraries.io/. GitHub repository is linked.

<sup>&</sup>lt;sup>8</sup>As presented in https://blog.podkalicki.com/.

In the initial phase, we need to generate the nonce(s). For testing purposes, we configure the process to accept an additional numeric parameter k so as to emulate multiple different ARs. The original code creates a single one with os.urandom(20); we call that function multiple times and store the four nonces in a list. Once the generation phase is complete, we log the nonces on the console and also send them to PRV over the serial port<sup>9</sup>. We utilise some special characters as delimiters to make it simpler for PRV to process the input. The reader may refer to Appendix C for a description of the data format.

A similar procedure is applied to the received report. Recall that as per design,  $report = \{Sign, res, N\}$  (see Appendix A). Hence, once the report arrives, we first check whether our k nonces are included in N and then build the nonce aggregate n'. The Python script already employs the hashlib library<sup>10</sup> to compute the original HMAC-SHA1. Instead, we will utilise the simple SHA-1 function. Namely, we define a method

#### 1 | def hash\_chain(list)

accepting a list and returning the SHA-1 digest yielded by hashing the elements of the list sequentially. We will use this method not only for the nonces, but for the memory compression as well.

For the next phase, we want to check the validity of the received res, that is, the compression of n' and the memory. In a real scenario, such as the SIMPL project, the valid memory state would be fetched from a database or some other type of storage. Since our testbench does not have such an entity at its disposal, we instead compute the expected memory state of PRV by utilising the flashed .hex file and the intelhex library<sup>11</sup>. We then use this variable together with the computed n' to calculate their SHA-1 compression (hash\_chain([intelhex, n'])) and compare it with res.

Subsequently, we need to check the digital signature. For this, we need a library providing ECDSA with the secp256k1 curve, exactly like in the case of PRV. Our library of choice is ultimately python-ecdsa<sup>12</sup>. Once again, in a real-world scenario, PRV will have distributed its ECDSA public key before the initiation of the RA process; however, here we have it statically stored in a variable public\_key. This allows us to check the received *Sign* against the received *res* (which we validated in the last step), and ultimately log the result on the console.

If any of the described checks fails, we log an error on the console and stop the RA process. Otherwise, should all of them succeed, we log that the attestation was successful.

# 5.5. Running the Project

The entire code is included on the disc provided with this work. In order to run it, the following is needed:

- An ATmega1284P-XPLD microcontroller. We provide no guarantees for other microcontrollers due to eventual pin differences that may raise the need for code modifications.

- A programmer in order to load the code. Our programmer of choice is the Atmel ICE (cf. Figure 5.2).

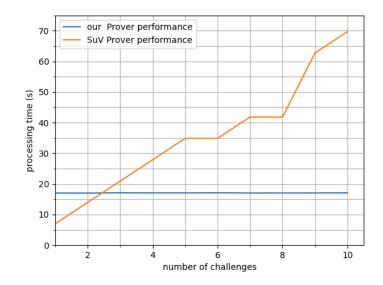

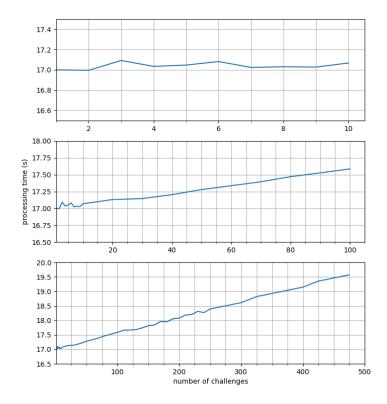

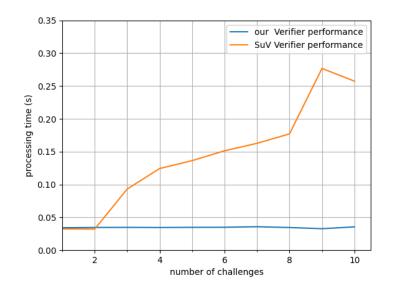

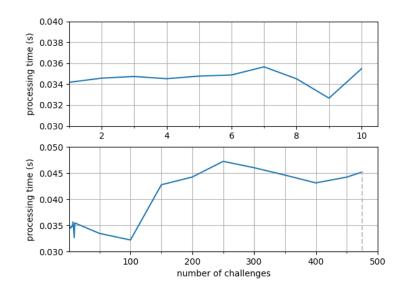

$<sup>^9{\</sup>rm For}$  the communication, VRF utilises the pySerial library. Documentation at https://pyserial.readthedocs.io/.