# Local Approximation of NFV Workloads

Master Thesis of

## Norbert Schmitt

At the Department of Computer Science Chair for Computer Science II Software Engineering

Reviewer: Second reviewer: Advisor: Second advisor:

Prof. Dr.-Ing. Samuel Kounev Prof. Dr.-Ing. Phuoc Tran-Gia M.Sc. Jóakim von Kistowski M.Sc. Piotr Rygielski

Duration: April 15th, 2016 - October 14th, 2016

I declare that I have developed and written the enclosed thesis completely by myself, and have not used sources or means without declaration in the text.

Würzburg, October 9, 2016

(Norbert Schmitt)

## Contents

| At | ostrac | t - German                                                                                                     | 1               |

|----|--------|----------------------------------------------------------------------------------------------------------------|-----------------|

| Ał | ostrac | t - English                                                                                                    | 3               |

| 1. | Intro  | oduction                                                                                                       | 5               |

| 2. | Fou    | ndations                                                                                                       | 7               |

|    | 2.1.   | Network Function Virtualization                                                                                | 7               |

|    | 2.2.   | Power Measurement and Methodology                                                                              | 9               |

|    |        | 2.2.1. Measurement                                                                                             | 9               |

|    |        | 2.2.2. Chauffeur                                                                                               | 12              |

|    | 2.3.   | Performance Counters                                                                                           | 13              |

|    | 2.4.   | Preexisting Worklets                                                                                           | 14              |

|    |        | 2.4.1. Pi Worklet                                                                                              | 15              |

|    |        | 2.4.2. XMLValidate                                                                                             | 15              |

|    |        | 2.4.3. SSJ                                                                                                     | 15              |

| 3  | Rela   | ted Work                                                                                                       | 17              |

| 5. |        | Energy Efficiency and Benchmarking                                                                             | 17              |

|    |        | NFV Deployment                                                                                                 | 18              |

|    |        | Power Estimation and Performance Counters                                                                      | 18              |

|    | •      |                                                                                                                | 10              |

| 4. | •••    | roach                                                                                                          | 19              |

|    | 4.1.   | Reference Workloads                                                                                            | 19              |

|    |        | 4.1.1. Local Workloads                                                                                         | 19              |

|    | 4.9    | 4.1.2. NFV Workload                                                                                            | 20              |

|    | 4.2.   | Workload Approximation       4.2.1.         Selection of Available Performance Counters       4.2.1.           | $\frac{20}{21}$ |

|    |        | 4.2.1. Selection of Avalable Ferformance Counters                                                              | $\frac{21}{23}$ |

|    | 43     | Regression Model                                                                                               | $\frac{23}{26}$ |

|    | т.0.   |                                                                                                                | 20              |

| 5. | •      | lementation                                                                                                    | 29              |

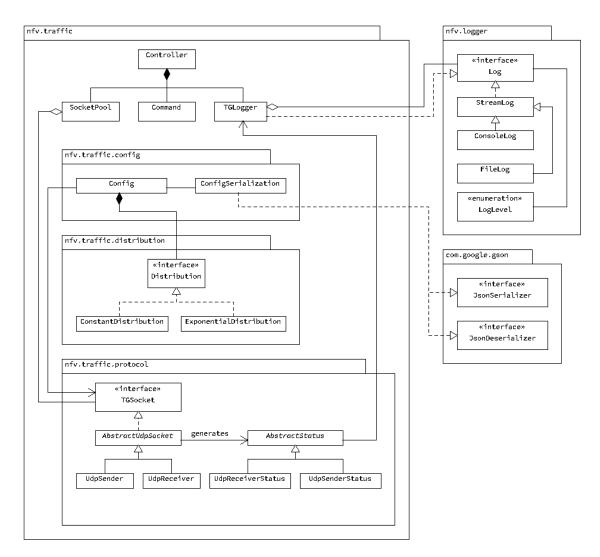

|    | 5.1.   | Traffic Generator and Receiver                                                                                 |                 |

|    |        | 5.1.1. Architecture                                                                                            |                 |

|    |        | 5.1.2. Configuration                                                                                           |                 |

|    | 5.2.   | NFV Workload                                                                                                   | 33              |

|    | 5.3.   | Linux Kernel Module                                                                                            | 33              |

|    |        | 5.3.1. Caching Modes                                                                                           | 33              |

|    |        | 5.3.2. Character Device Driver                                                                                 | 34              |

|    | 5.4.   | Relevant Performance Counter                                                                                   | 35              |

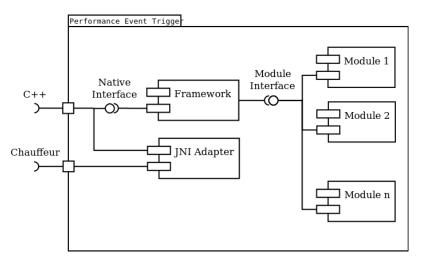

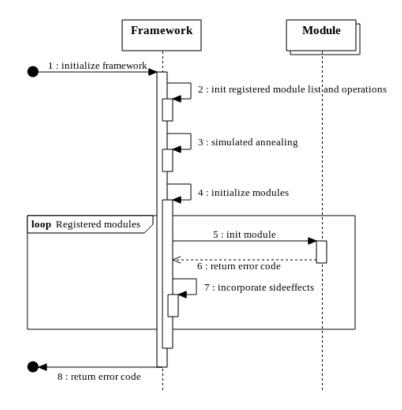

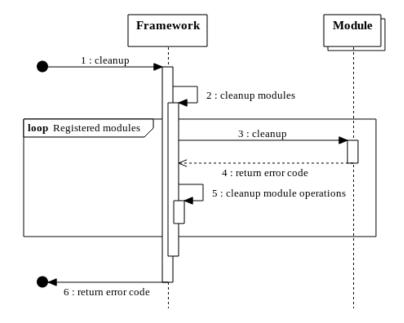

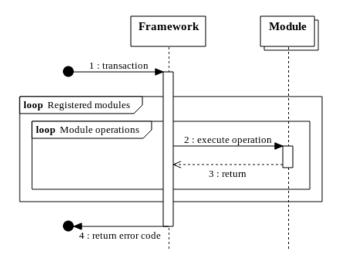

|    | 5.5.   | Performance Event Trigger Framework                                                                            | 39              |

|    |        | 5.5.1. Architecture                                                                                            | 39              |

|    |        | 5.5.2. Configuration $\ldots$ | 43              |

|     |          | 5.5.3.<br>5.5.4. | PET Build System                               | $\begin{array}{c} 45\\ 47\end{array}$ |

|-----|----------|------------------|------------------------------------------------|---------------------------------------|

| 6   | <b>T</b> | had Ca           | <b>A</b>                                       | 49                                    |

| 0.  |          | bed Se           | nce Testbed and Calibration                    | <b>49</b><br>49                       |

|     |          |                  | feur Testbed                                   | $\frac{49}{52}$                       |

|     | 0.2.     | Chaun            |                                                | 52                                    |

| 7.  | Eval     | uation           |                                                | 53                                    |

|     | 7.1.     | Perform          | mance Counter Implementation                   | 53                                    |

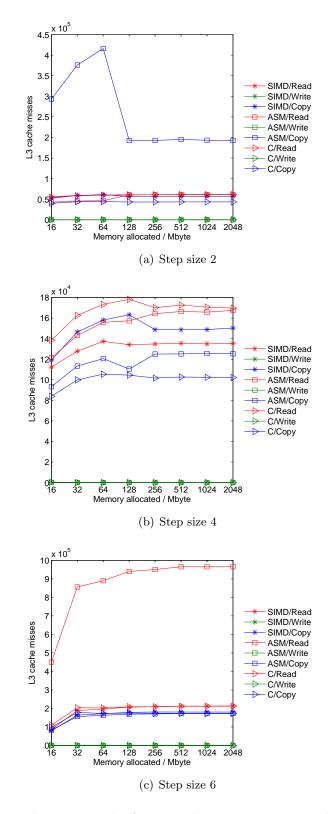

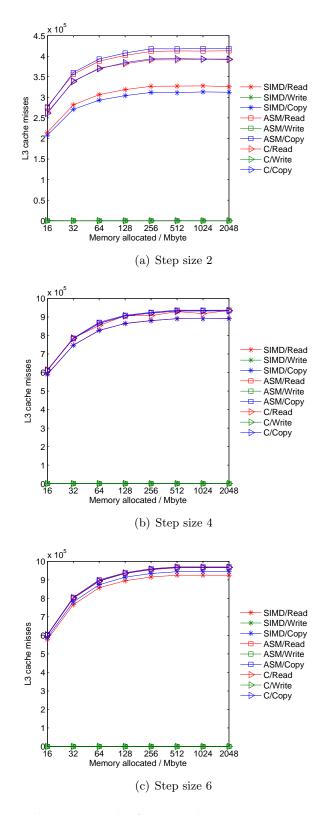

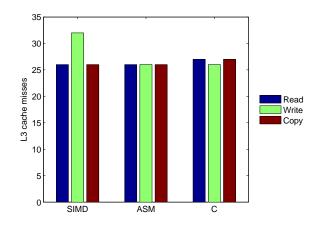

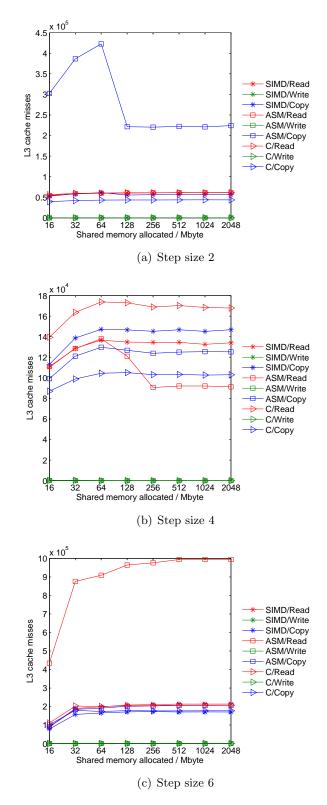

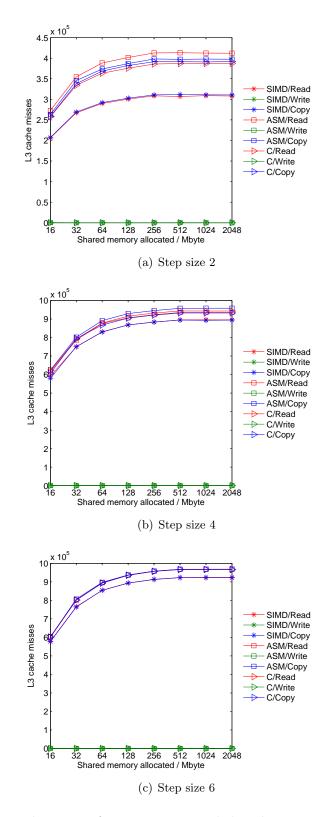

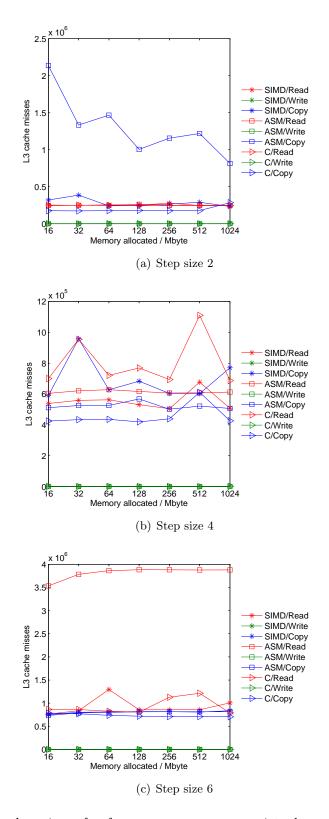

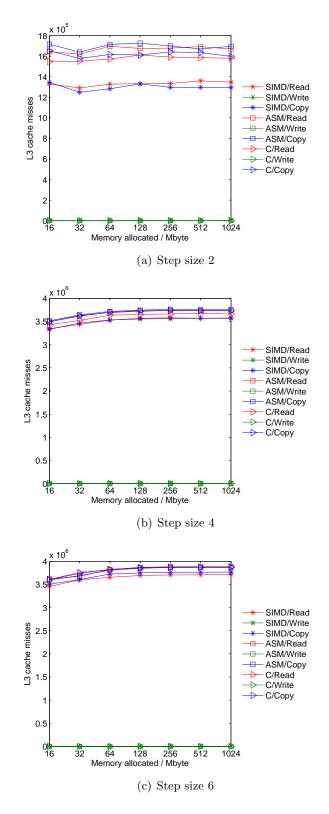

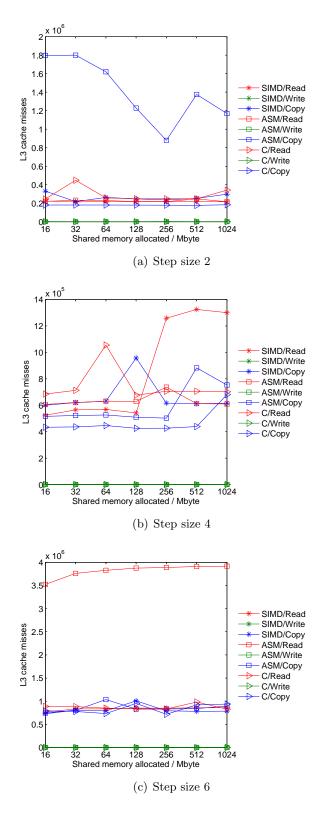

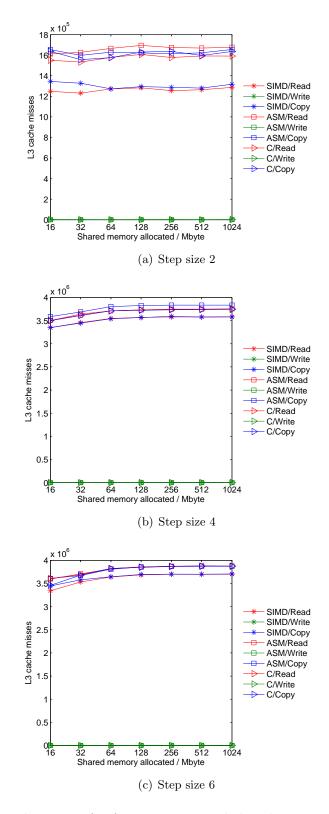

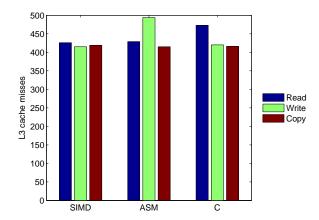

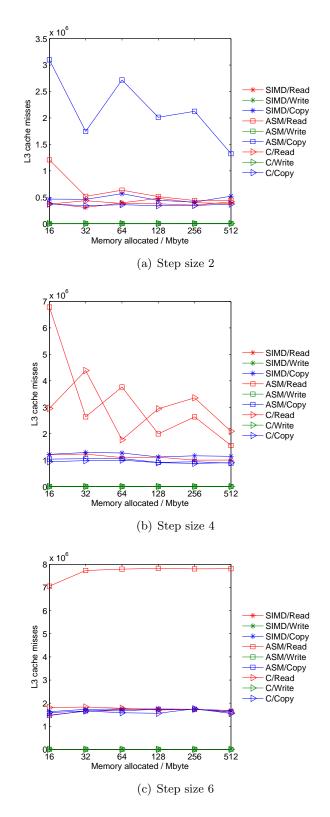

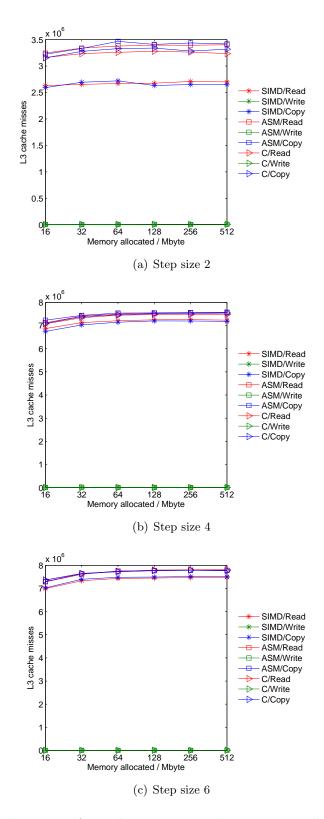

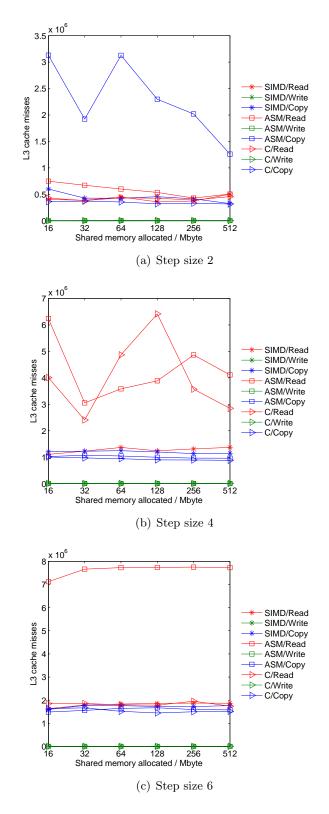

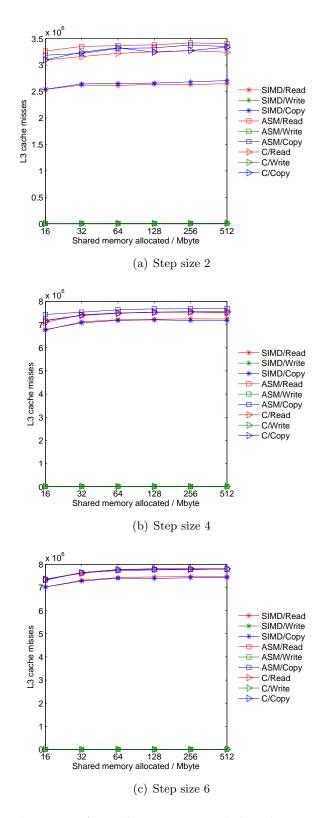

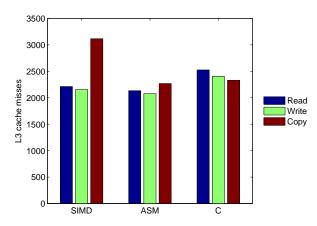

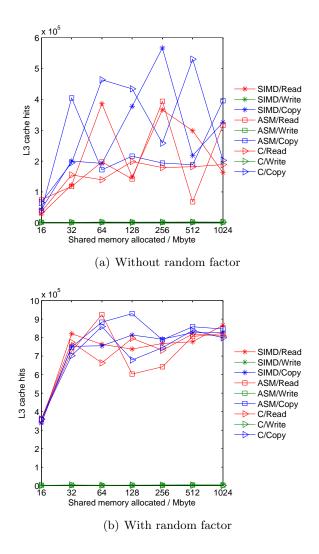

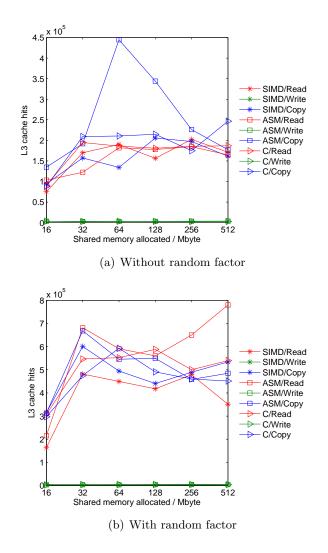

|     |          | 7.1.1.           | L3 Cache Misses                                | 54                                    |

|     |          | 7.1.2.           | L3 Cache Hits and L2 cache misses              | 58                                    |

|     |          | 7.1.3.           | L2 Cache Hits                                  | 61                                    |

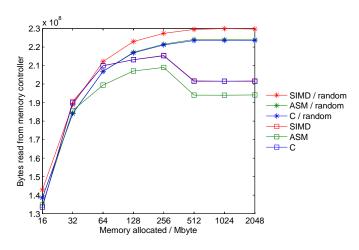

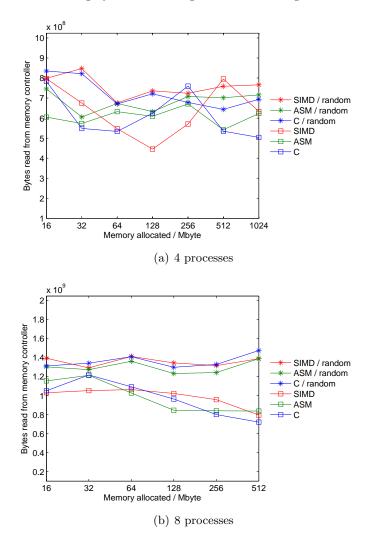

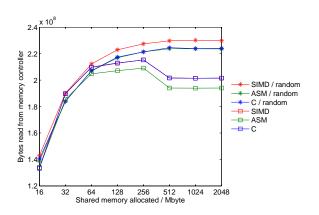

|     |          | 7.1.4.           | Bytes Read from Memory Controller              | 61                                    |

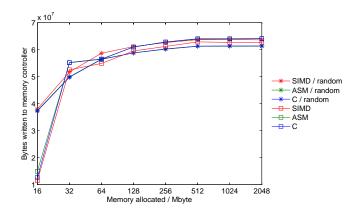

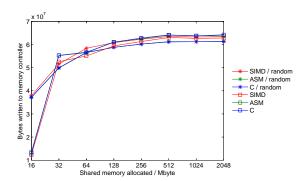

|     |          | 7.1.5.           | Bytes Written to Memory Controller             | 65                                    |

|     |          | 7.1.6.           | Instructions Retired                           | 68                                    |

|     |          | 7.1.7.           | Context Switches                               | 69                                    |

|     |          | 7.1.8.           | Interrupts                                     | 70                                    |

|     | 7.2.     | Perform          | mance Event Trigger Framework                  | 71                                    |

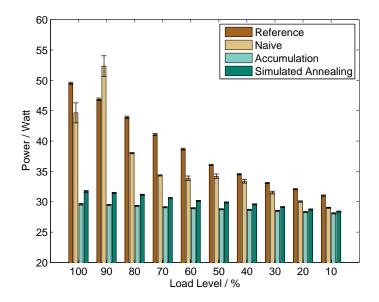

|     |          | 7.2.1.           | Pi Workload                                    | 72                                    |

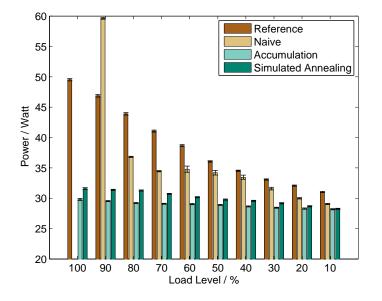

|     |          | 7.2.2.           | XMLValidate                                    | 75                                    |

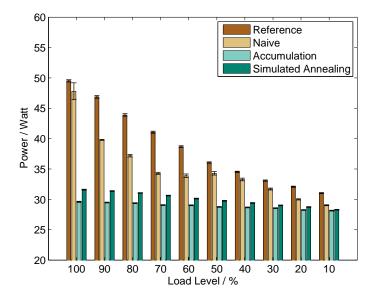

|     |          | 7.2.3.           | SSJ                                            | 77                                    |

|     |          | 7.2.4.           | NFV Workload                                   | 79                                    |

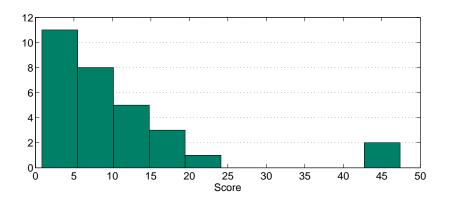

|     |          | 7.2.5.           | Lower Bound for Valid Measurements             | 84                                    |

|     | 7.3.     | Linear           | Regression Model                               | 85                                    |

| 8.  | Con      | clusion          |                                                | 89                                    |

|     | 8.1.     | Future           | e Work                                         | 90                                    |

| Bi  | bliogi   | raphy            |                                                | 93                                    |

|     | -        |                  |                                                | 00                                    |

| LIS | St Of    | Figures          |                                                | 99                                    |

| Lis | st of    | Tables           |                                                | 101                                   |

| Ap  | pend     | lix              |                                                | 103                                   |

|     | A.       |                  | Background Noise                               | 103                                   |

|     | В.       | Testbe           | ed Hardware                                    | 103                                   |

|     |          | B.1.             | SUT                                            | 103                                   |

|     |          | B.2.             | Traffic Generator and Receiver                 | 104                                   |

|     | С.       | Measu            | rement Results of Selected Performance Counter | 105                                   |

|     | D.       | PET S            | Side Effect Configuration                      | 120                                   |

|     | Е.       |                  | rement Results of PET                          |                                       |

|     | F.       | Linear           | Regression Model                               | 124                                   |

| Ac  | rony     | ms               |                                                | 125                                   |

## Abstract - German

Mit dem zunehmenden Bedarf an Energie für die moderne IT Infrastruktur wird die Wahl effizienter Geräter immer wichtiger. Die SPEC stellt für diese Zwecke standardisierte Benchmarks bereit, die die Energieeffizienz messen. Zur Beurteilung der Energieeffizienz sind verlässliche Messungen realer Anwendungen notwendig. Durch die zunehmende Vernetzung von Systemen werden zuverlässige Messungen komplexer, da Software externe Eingaben benötigen kann um das Testsystem auszulasten. Dies kann unter anderem dazu führen, das Komponenten ausgelastet werden die unter anderen Workloads untätig sind und den Verbrauch reduzieren oder keinen Strom verbrauchen.

Zusammen mit dem steigenden Trend in Richtung Software Defined Networking (SDN) und Network Functions Virtualization (NFV), der Virtualisierung dedizierter Geräte als Softwarelösungen auf handelsüblichen Servern, erschwert die zuverlässige Messung extern unter Last gesetzter Software zusätzlich und erhöht die Fehleranfälligkeit.

In dieser Arbeit wird deshalb das Performance Event Trigger Framework (PET) vorgestellt. Um das Testsystem unter verschiedenen Laststufen zu betreiben und den Stromverbrauch zu approximieren löst es Performance Events aus. Das Framework ist als Chauffeur Bechmark konzipiert um eine einfache Nutzung zu gewährleisten. Zuerst werden die Performance Counter anhand der Korrelation mit dem Stromverbrauch ausgewählt und die Implementierung der Auslöser vorgestellt. Jeder Auslöser wird darauf auf seine Genauigkeit hin untersucht und in das Framework eingepflegt. Das Framework wird danach durch drei Workloads, dem Pi Workload aus Chauffeur, XMLValidate und SSJ aus SERT, evaluiert um die Machbarkeit und Genauigkeit der Approximation zu zeigen. Um zu zeigen das PET auch extern unter Last gesetzte Workloads annähern kann, wird ein vierter NFV Workload in Form einer DPI Firewall verwendet. Zusätzlich wird ein lineares Regressionsmodell erstellt zur weiteren Auswertung.

Es konnte im Rahmen der Arbeit gezeigt werden, dass die Näherung von Workloads anhand von Performance Countern möglich ist und das PET eine durschnittliche Genauigkeit von unter 10% erreicht.

## Abstract - English

With the growing demand of energy in modern IT infrastructure, selecting more efficient devices becomes more important as well. Standard benchmarks are provided by the SPEC to measure the energy efficiency. Assessing the energy efficiency requires reliable measurements of real world applications. Due to the rising connectivity between systems, reliable measuring energy efficiency becomes difficult. Workloads relying on external input might stress hardware components of a system which would otherwise lie dormant and reduce their consumption or not using any power at all.

Together with the rising trend of Software Defined Networking (SDN) and Network Functions Virtualization (NFV), virtualizing dedicated appliances as software running on offthe-shelf servers, reliable measuring efficiency on externally driven workloads becomes even more challenging and error prone.

This thesis therefore proposes the Performance Event Trigger Framework (PET). It triggers performance events to approximate a workload, which normally needs external devices to run the System Under Test (SUT) under different load levels. The framework is implemented as a Chauffeur benchmark to allow for easy use. First the performance counters that have a high correlation with power consumption are selected and an implementation to trigger these events is presented. Each event trigger is then evaluated in terms of accuracy and incorporated in the final framework. The framework itself is evaluated against three workloads, the Pi workload from Chauffeur, XMLValidate and SSJ from SERT to show the feasibility and accuracy of the approximation. A fourth NFV workload in form of a DPI firewall is also evaluated to show that PET can approximate externally driven loads. A linear regression model is also used as a second mean of evaluation if PET is able to approximate workloads.

In the course of this thesis it has be shown that approximating workloads with performance counters works and that PET has a reasonable accuracy, with average deviation of less than 10%.

## 1. Introduction

Efficiency is a growing concern in today's IT infrastructure. In 2006 data centers in the United States consumed an estimate of 61 billion kWh annually. The energy consumption has risen to an estimated 93 billion kWh in 2013 and is projected to climb to 140 billion kWh by 2020, according to the National Resources Defense Council (NRDC) [WD14]. With the rising amount of servers and therefore energy consumption, the demand for network equipment will climb as well.

Reducing the power consumption and improving energy efficiency requires reliable measurements of real world applications the servers are executing. With increasing connectivity and dependencies between different applications, reliably measuring energy efficiency becomes difficult as benchmarks lack the ability to stress hardware components only used by interconnected workloads. The workloads must be driven by external load generators.

Virtualization, a growing paradigm in IT, transferred into the networking infrastructure with the introduction of Software Defined Networking (SDN) and later Network Functions Virtualization (NFV) in 2013. Therefore the energy efficiency of virtualized networks has become a considerable issue as well.

Often performance counters are used to estimate the power consumption of a system. Also the modeling via performance counters is widely researched. Yet the current use case scenarios for performance counter lack the ability for experimental measurements in case a workload is dependent on external appliances.

A lot of effort has been put into making data centers more energy efficient. One aspect is the measurement of server energy efficiency with the Server Efficiency Rating Tool (SERT), developed by Standard Performance Evaluation Corporation (SPEC) [LTA<sup>+</sup>12]. Rating the energy efficiency through benchmarking helps to provide an aid in selecting the most efficient server for the intended service or workload. Yet the SERT can only run locally and not stress hardware that would otherwise be used by workloads driven through external requests, such as a Virtual Network Function (VNF). This unused hardware could become active in real world scenarios and influence hardware components already evaluated for energy efficiency, which leads to a change in power consumption and hence reduced efficiency. Rating the energy efficiency of externally driven workloads also demands a more complex testbed as the load generators must be considered in the benchmark design. As a consequence, measurements and setup are more time consuming and error prone.

As modern servers are working under highly variable load intensities [vKHK14] and a server is not generally more efficient under full load [vKBB<sup>+</sup>15], benchmarking the server

under different load levels is necessary for a complete energy rating. Auto calibrating a load level aware benchmark that needs to be driven externally is challenging and not supported by the SERT. Additionally, external power meters used for power measurements need stable loads for higher accuracy [LT11]. Therefore the normally used workloads are often not suitable.

A lot of work has been done in terms of energy efficiency benchmarking and modeling. Often established benchmark suites like SPEC are used to achieve comparable results. Yet externally driven workloads are not part of these suites. In the NFV context, benchmarking is mostly focused on a broader scope, taking into account networks consisting of several entities while this thesis aims to abolish the need for complex interacting systems.

Models based on performance counters work, but mostly use local workloads for validation. If the models can predict highly interconnected applications accurately needs to be determined. Other works on performance counters only focus on the counters themselves and their accuracy and overhead for making them available to the user and not on how an accurate counter value can be achieved by deliberately triggering them.

To be able to measure energy efficiency of a complex workload that is request driven, the implementation and evaluation of a local approximation is proposed. It has been shown through models that performance counters and power consumption can be correlated. As a result, performance counter events, generated through software implementations, will be used to modify the counters accurately and achieve a power consumption approximation. The proposed approach remedies the need for external load generators, making efficiency measurements on externally driven workloads possible and simplifies the test setup. It can also be used to validate power or efficiency models on more complex workloads. The resulting software should be modular to make the framework extensible for future implementations of performance event triggers.

Before the proposed framework can be implemented, the correlation between the available performance counters and power consumption are calculated and optimal counters are selected. Multiple implementations and configurations for each counter are evaluated to determine the accuracy of triggering events and side effects on other counters. After the identification of the optimal implementations, the framework is created and evaluated against reference workloads. The reference workloads consist of a simple benchmark and workloads from the SERT as well as an externally driven workload in form of a Deep Packet Inspection (DPI) firewall (VNF). During all measurements, power consumption and the performance counters are measured and compared to the reference workloads. A regression model is used as a second validation method to test if the framework can accurately approximate externally driven workloads.

## 2. Foundations

This chapter introduces the required foundations for this thesis. First NFV is introduced to give an overview of its components. Afterwards a short description of the SERT measurement methodology is given on how measurements in this thesis are taken. This section also contains a description of the Chauffeur power and performance benchmarking application used as test harness. An introduction to performance counters and the IntelPCM tool used for instrumentation is provided. The chapter finishes with an explanation of preexisting workloads used for evaluation.

## 2.1. Network Function Virtualization

NFV describes the virtualization of network functions normally carried out by dedicated network appliances. Using dedicated hardware has certain drawbacks as stated by [CCW<sup>+</sup>12]. These include increasing costs of energy, decrease in hardware life cycles due to innovation and rare skills needed to integrate and operate highly specialized equipment.

It was introduced to counter the negative aspects by performing the network functions not on dedicated hardware but in software. The software can then be deployed more easily on commodity hardware. Configuration of a network and its functions is faster and easier as the software components of a NFV, the VNFs, can be remotely deployed without having to switch out network appliances at location. This makes it suitable for a wide range of use cases in the data and control plane as explained in [CCW<sup>+</sup>12].

The European Telecommunication Standardisation Group (ETSI) provides several use cases that benefit from having network functions virtualized instead of dedicated devices as stated in [ETS13].

- Network Functions Virtualization Infrastructure as a Service

- Virtual Network Function as a Service (VNFaaS)

- Virtual Network Platform as a Service (VNPaaS)

- VNF Forwarding Graph

- Virtualization of Mobile Core Network and IP Multimedia Subsystem (IMS)

- Virtualization of Mobile base station

- Virtualization of the Home Entertainment

- Virtualization of Content Delivery Networks (CDNs) (vCDN)

- Fixed Access Network Functions Virtualization

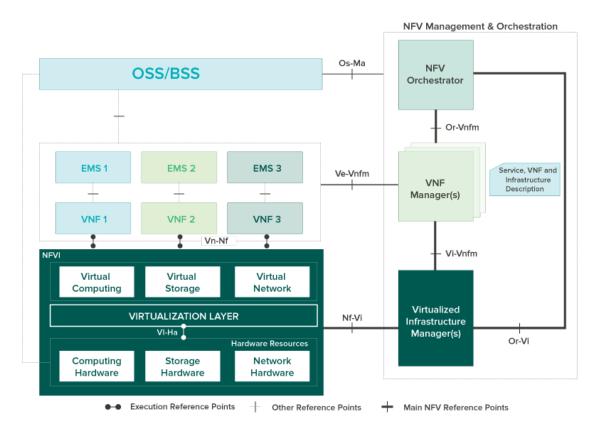

According to [ETS14], NFV consists of the following components. The main parts and interaction with each other can be seen in Figure 2.1.

#### 1. **NFVI**

Network Functions Virtualization Infrastructure (NFVI) is providing computational and virtualization resources for NFV to execute VNFs. The host for VNFs can be any device capable of hosting a Virtual Machine (VM) but is usually a commodity server.

2. **VNF**

This is the software network function that can be executed in a VM like Network Adress Translation (NAT), load balancing or firewalling.

#### 3. NFV Management and Orchestration

Administration tools and protocols for the NFVI as well as VNFs. It is able to deploy new VNFs and reconfigure, migrate and monitor running Virtual Network Function Instances (VNFIs).

### 4. Operation Support System (OSS)/Business Support System (BSS)

The OSS or BSS is operating and managing the supporting systems of the NFV. Such as the physical network or SDN.

Figure 2.1.: NFV architecture as taken from [OPN]

The main component for this thesis is the VNF, in the form of a simple DPI firewall. This specific exemplary workload is selected as it stresses the System Under Test (SUT)'s Network Interface Cards (NICs). A NIC is a component usually not targeted by locally running workloads. To determine the influence of externally activated hardware on the proposed approximation, the DPI firewall is selected as request driven reference workload.

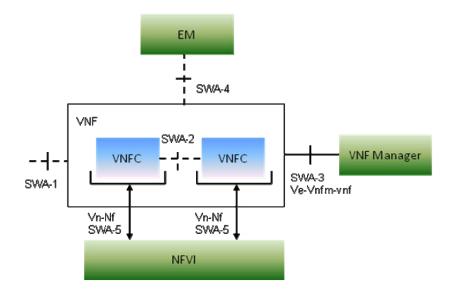

An instance of a VNF deployed by a VNF Manager is referred to as VNFI. It can either be executed in a virtualized environment or directly on hardware. If executed virtualized, then each VNFI runs in its own virtualized container. VNFs are the basic building blocks of a NFV. A VNF can be build out of several Virtual Network Function Components (VNFCs) as shown in Figure 2.2 or as a single entity. If a VNF is build from multiple VNFCs, their internal interfaces do not need to be exposed. The VNF on the other hand has a well-defined interface to other network functions which can be either VNFs themselves or dedicated appliances. The implemented outside interface is defined by standardization organizations like the 3rd Generation Partnership Project (3GPP) or the Internet Engineering Task Force (IETF).

Figure 2.2.: VNF functional view, taken from [ETS14]

The requirements for a VNF deployment are described in the Virtual Network Function Descriptor (VNFD) of which each VNF has exactly one. The VNFD also includes descriptions of performance, security, reliability and other non-functional assurances as stated in [ETS14].

### 2.2. Power Measurement and Methodology

This section describes how measurements are taken. It is based on Power and Performance Benchmark Methodology [SPEb] and the Server Efficiency Rating Tool Design Document [SPE13] by SPEC. While SERT in its entirety itself is not used in this thesis, its guidelines on how energy efficiency is measured still apply to keep the measurements comparable as SERT is used as regulatory standard by the United States Environmental Protection Agency (EPA). It is also adopted by the industry like the SAP benchmark and Transaction Processing Performance Council (TPC) [SAP11] [PNV<sup>+</sup>10]. Most measurements are performed with the help of Chauffeur, which allows to automatically calibrate and run the workload at different load levels.

#### 2.2.1. Measurement

All measurements in this thesis follow the methodology introduced by SPEC for benchmarks capable of graduated throughput levels. Throughput is defined as the number of transactions executed in a fixed time frame. A transaction is one work package processed by the benchmarked workload. In case of the DPI firewall, one transaction equals one network package inspected. Transactions must have blocking behavior to get feedback during measurements of the number of transactions executed.

Benchmarks using graduated throughput levels request a steady state of transactions performed during a fixed time period. The steady state is enforced through the benchmark harness or the benchmark itself. The throughput levels are also referred to as load levels.

The sequence for such a benchmark is as follows, cited from [SPEb]:

- 1. System is made ready for measurement.

- 2. Harness starts environmental measurements

- 3. If required, initiate calibration process to determine maximum throughput

- 4. Compute intermediate measurement targets relative to maximum throughput

- 5. Iterate:

- a) Harness starts benchmark segment run at throughput interval X, where X begins at the highest target throughput and reduces each iteration until a zero-throughput interval can be measured, to obtain an Active-Idle measurement

- b) Delay as needed for benchmark synchronization and to achieve steady state

- c) Harness starts power measurements

- d) Harness or benchmark collects power and performance metrics.

- e) Harness ends collection of performance and power measurements

- f) Delay as needed for benchmark synchronization

- g) Benchmark segment completes

- h) Harness delays as needed for synchronization

- 6. Harness ends environmental measurements

- 7. Harness post-processes performance and power data

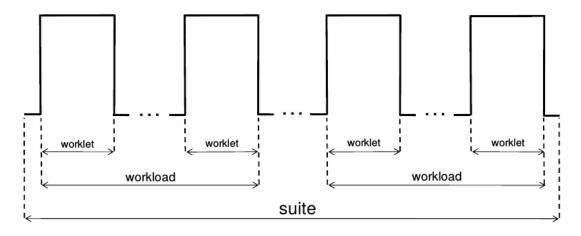

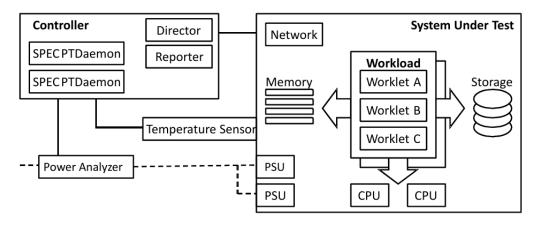

The basic SERT components are illustrated in Figure 2.3. The SERT test suite consists of different benchmarks, called worklets. The worklets dispatches transactions to put the SUT under load. These worklets are grouped together in workloads. Workloads are designed to stress certain aspects or components of the SUT. The contained worklets are run in a defined sequential order. All workloads together comprise the test suite and are also run sequentially. A worklet can also have a sequence of multiple different transactions. The transactions in a worklet sequence are executed one after another in a fixed order.

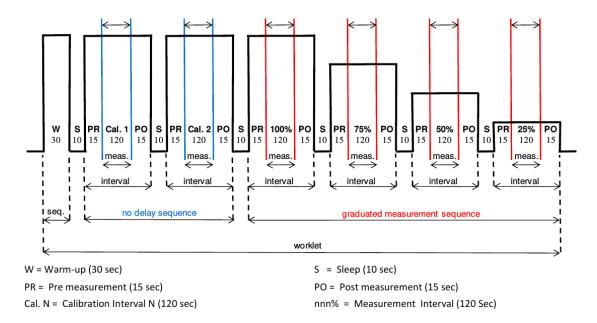

Worklets are further divided into three sequences as shown in Figure 2.4. First the *warmup* sequence, secondly the no delay sequence or calibration and finally the graduated measurement sequence which stresses the SUT under the defined load levels. The warmup and calibration sequences are optional to a worklet.

Each sequence is divided into intervals. An interval is comprised of three phases. The first phase is the *pre-measurement*, which lets the SUT settle for the current load level and reduce influences of oscillating startup behaviors of certain hardware or software components. In the next phase, *measurement* or *recording*, power measurements are taken and the actual throughput is measured. An interval finishes with the *post-measurement* phase. Each phase runs for a fixed time frame.

Figure 2.3.: SERT components, as taken from [SPE13]

Figure 2.4.: Worklet measurement execution, taken from [SPE13]

SPEC allows several methods for calibrations, as long as the benchmark can be run consistently over the measurements. Four options are pointed out specifically by [SPEb]. The first three are of special interest because they allow for automatic calibration. The fourth option is for engineering and academic environments.

- The benchmark is run once at maximum throughput. The actual resulting throughput is used as maximum.

- The benchmark is run 2 to *n* times and the last two runs are averaged. The resulting value is the maximum throughput.

- The benchmark is run multiple times until the last runs result is lower then the preceding one. If this is the case, run the benchmark a last time and average over the last three runs to compute the maximum.

- Set the maximum throughput to an arbitrary fraction of the benchmark run.

As part of this thesis is to simplify testbeds for externally driven loads, including autocalibration, the fourth option is not selected. Because the SERT uses the second option and to evaluate the proposed framework as closely to existing benchmark runs as possible, the second option is selected.

#### 2.2.2. Chauffeur

Chauffeur is used as a test harness and this section is mainly based upon the Chauffeur<sup>TM</sup> Worklet Development Kit (WDK) User Guide [SPEa] and [LAB<sup>+</sup>13]. Chauffeur incorporates the aforementioned measurement methodology and is also used by the SERT. It is designed with the following principles in mind.

- Energy Measurements

- Scalability

- Ease of use

- Portability

- Flexibility

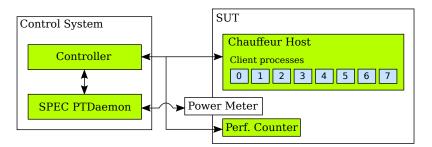

Figure 2.5 shows an overview of Chauffeur. It consist of the following hardware (HW) and software (SW) parts:

Figure 2.5.: Chauffeur overview from [SPEa]

| Controller (HW)           | The controller system governs which sequence is run and for<br>how long. It also collects the measurement data. It com-<br>municates with the SUT and Power Analyzer via TCP/IP. |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUT (HW)                  | The actual system stressed during measurements.                                                                                                                                  |

| Power Analyzer (HW)       | Measures the power consumption of the SUT.                                                                                                                                       |

| Temperature Sensor (HW)   | Measures the ambient temperature in the SUT's vicinity.                                                                                                                          |

| <b>SPEC PTDaemon</b> (SW) | Collects the power and temperature measurements from<br>the Power Analyzer and Temperature Sensor.                                                                               |

| <b>Director</b> (SW)      | Controls the measurement sequence on the SUT.                                                                                                                                    |

| Reporter (SW)             | Receives all results from a measurement and compiles a report of the benchmark suite.                                                                                            |

| Workload (SW)             | Actual workload stressing the SUT. It is controlled by the Director.                                                                                                             |

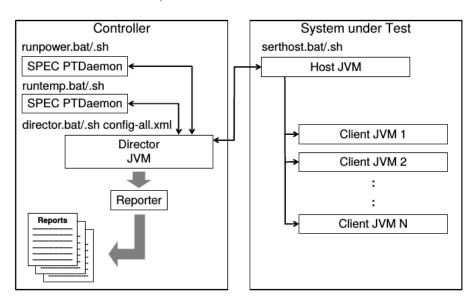

The Chauffeur components and communication are illustrated in Figure 2.6. The Director runs as a Java Virtual Machine (JVM) on the controller and communicates with the SPEC PTDaemon to collect power measurement results. It also controls the Host JVM which in turn runs the Clients. Chauffeur can be configured to run the workload on several Central Processing Unit (CPU) cores in parallel. For each core it should run on, a Client JVM is started by the Host which actually runs the workload and worklets, and dispatches transactions until the current interval is finished. The results are collected and send to the Director, which is handing them on to the Reporter compiling the final reports. All communication is done via TCP/IP.

Figure 2.6.: Chauffeur components and communication from [SPEa]

## 2.3. Performance Counters

This thesis tries to model a workload's power consumption locally by generating performance counter events. Performance counters are integrated in today's hard- and software and can be read with either specialized software like IntelPCM, performance monitoring utilities of the Operating system (OS) or manually by directly accessing CPU registers. This chapter will first give an introduction of what performance counters are and some drawbacks associated with them. Afterwards the counters available on the SUT are listed in their respective sections of either CPU counters which are read with IntelPCM or operating system counters that will be read by using the Linux virtual filesystem proc. This work focuses on performance counters available on Intel platforms due to the available testbed which uses an Intel Xeon E3-1230 v5.

The following descriptions are based on [Int16b] and [AMD16]. To monitor a systems performance and behavior, hardware manufacturers including Performance Monitoring Units (PMUs) for observation. A PMU includes Model Specific Registers (MSRs) which can store the count for either of the two event types:

- Occurrence event counts the number how often an event has been observed.

- Duration event counts the accumulated clocks for which an event has been observed.

Performance counters are further divided into two different classes, *architectural* and *non-architectural*. Architectural counters are a smaller subset of events as they are available across processor implementations. Non-architectural counters offer a wider variety of countable events but are model specific and therefore might not be available on certain systems.

The PMU also includes a Pin Control (PC) flag to toggle Performance Monitoring (PM) pins (PM0/BP0 or PM1/BP1) if an event occurs or an MSR overflows. PM events cover a broad scope on what the hardware is currently doing, which includes for example, but is not limited to, cache hits or misses on each cache level, falsely or correct predicted branches and instructions retired. The recorded performance counter events can be read on a system wide basis. Subsets can also be read on a per socket or a per core basis.

Monitoring performance events using a PMU does have its disadvantages. Weaver et al. [WTM13] have shown that modern implementations of performance counters are not accurate and have a tendency to deviate. They found two causes of deviation that make interpreting performance counters a difficult task. One cause is *nondeterminism* in which identical workloads resulted in different counter values and *overcount* for which counters where increased multiple times for the same instruction. Another problem presents itself if the PM pins are used. For occurrence events, it might be possible that an event happens twice within one clock cycle. While the value in the MSR is incremented twice, the pin is only asserted once which causes a deviation.

IntelPCM is a tool provided by Intel for monitoring performance counters. It can either be executed as a standalone application or integrated into a program using its C++ Application Programming Interface (API). As reading performance counters requires careful implementation, IntelPCM is selected as tooling to minimize errors resulting from erroneous self implemented instrumentation.

The operating system itself also counts certain events that can be obtained. In the case of Linux, these counters can be read from the virtual proc file system. Especially the files /proc/stat and /proc/meminfo are of interest. They, for example, give insight on how many hard and software interrupts have been processed, the number of context switches performed and memory utilization.

## 2.4. Preexisting Worklets

For evaluation, three readily available worklets are selected as a basis to test if the framework works for approximating local applications. They were selected as they stress different hardware parts of the SUT. The first worklet described in this section is the  $\pi$  worklet, approximating  $\pi$ . It was selected as it gives a first evaluation if the proposed framework can approximate simple workloads and using performance counters is a viable approach. The Pi worklet is followed by XMLValidate from the SERT which stresses the CPU and memory, making it more complicated, provoking more counters to be triggered to validate the framework with a wider variety of performance counters. The last worklet described is the hybrid SSJ worklet, also from the SERT. It is closest to a real world application and combines different worklets stressing a more diverse set of hardware components. The evaluation of this workload will show if the framework can approximate locally running workloads reasonably well before evaluating externally driven workloads.

#### 2.4.1. Pi Worklet

The Pi worklet comes from the ChauffeurTest package shipped together with Chauffeur. It calculates  $\pi$  with an iterative approximation using the Gregory-Leibniz series shown in 2.1. The upper limit for n is set randomly for each transaction with values between [1000; 100000]. This worklet is especially heavy on the CPU but not other hardware components of the SUT. It is therefore a good basis worklet for a first evaluation if the proposed framework is feasible.

$$\pi = 4 \cdot \sum_{k=1}^{n} \frac{(-1)^{k+1}}{2k-1} \tag{2.1}$$

#### 2.4.2. XMLValidate

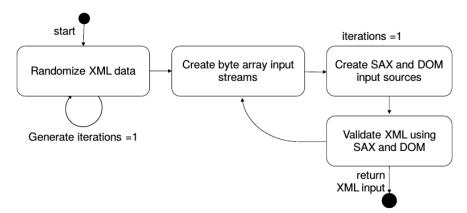

The XMLValidate worklet, as described in [SPE13], uses the Java javax.xml.validation package to implement transactions. The worklet validates Extensible Markup Language (XML) files against a XML schemata as shown in Figure 2.7. It randomizes the input file by swapping commented regions within the XML file. Despite used as a CPU benchmark, it also stresses the memory subsystem. It also performs a more complex operation than the Pi worklet. XMLValidate is used as feasibility evaluation when the memory system is stressed as well.

Figure 2.7.: XMLValidate transaction from [SPE13]

#### 2.4.3. SSJ

SSJ from the SERT test suite simulates Online Transaction Processing (OLTP) as a Server Side Java application. It is described in [SPE13] and based on SSJ in SPECpower\_ssj2008 but is not comparable to it. SSJ is a hybrid worklet, which means it is stressing multiple

components of the SUT. The CPU, caches and memory of the SUT are stressed. This worklet is closer to a real world application than the Pi or XMLValidate worklets. It is therefore raising the complexity in the evaluation of the proposed approach.

The SSJ worklet includes six transactions as a worklet sequence which are executed with certain frequencies as cited from [SPE13]. The mentioned frequencies are approximations how often a transaction occurs.

| New Order $(30.3\%)$          | A new order is inserted into the system            |

|-------------------------------|----------------------------------------------------|

| <b>Payment</b> $(30.3\%)$     | Records a customer payment                         |

| <b>Order Status</b> $(3.0\%)$ | Requests the status of an existing order           |

| <b>Delivery</b> $(3.0\%)$     | Processes orders for delivery                      |

| Stock Level $(3.0\%)$         | Finds recently ordered items with low stock levels |

| Customer Report $(30.3\%)$    | Creates a report of recent activity for a customer |

## 3. Related Work

A number of work has been in done in terms of energy efficiency, power consumption, NFV performance counters. These topics often overlap. The following chapter will give an overview on the specified topics. First the aspect of efficiency measurements and improvements, followed by a short overview of work on NFVs. Finally a summary of performance counter and their usage in power estimation and modeling is presented.

## 3.1. Energy Efficiency and Benchmarking

A wide variety of work has been done in terms of energy efficiency benchmarking with a focus on CPU loads and NFVs. Most work focuses on a broader scope like [vKBL<sup>+</sup>15], in which workloads are distributed hierarchically from multiple machines down to Simultaneous Multithreading (SMT) and also Bagaa et al. [BBLM14], which distributes VNFs efficiently while also taking SDN into account. Botero et al. [BHD<sup>+</sup>12] developed a Mixed Integer Program (MIP) for consolidating VNFs in a virtualized network to achieve better energy efficiency. A. Beloglazov and R. Buyya [BB10] improve efficiency by migrating VMs within a data center while ensuring Quality of Service (QoS). However, in the aforementioned works, the efficiency is only viewed in the scope of a complete network, taking into account several systems or VNFs instead of a single entity.

Work from Jin et al. [JWC12] concentrates on the trade-off between the virtualization overhead and efficiency increase using VMs by aggregating workload on fewer physical machines with higher utilization. Yet using less systems does not necessarily increase efficiency, as shown in [vKBB<sup>+</sup>15], in which the efficiency of the SERT CPU workloads under different load levels is measured. It also explores the influence of different workloads on efficiency. The proposed solution on the other hand tries to simulate workloads on a lower level without the need to approximate multiple connected systems.

A more focused paper [vKBB<sup>+</sup>16] shows that repeatable power measurements can be difficult to achieve and measurement results can vary, even with nominally identical CPUs. Yet this thesis is not only measuring CPU efficiency but rather a complete system, in which the CPU is only one of many components influencing the efficiency.

It is evident that this thesis is in between both categories of having a broad view of connected systems and focusing on specific components.

### 3.2. NFV Deployment

Work on NFVs focuses often on scaling a NFV to provision for dynamically changing demands. The work of Moens and DeTurk [MDT14] as well as Mijumbi et. al. [MSG<sup>+</sup>15] are concerned with deploying VNFs in virtualized environments. While both develop models and algorithms for efficient VNF placement, they do not take into account power consumption. In an article from Bouet et. al. [BLCC15] a cost minimization heuristic is developed which takes different aspects of VNF placements into account. Yet the energy efficiency or power consumption, a central part of this thesis, is not addressed.

### 3.3. Power Estimation and Performance Counters

Performance counters are used for performance analysis of software. One way for such an analysis is calculating Call per Instructions (CPIs) stacks. In a paper from S. Eyerman et al. [EEKS06] performance counters are used to calculate more accurate stacks on superscalar out-of-order processors. They use different miss events like cache misses and Translation Lookaside Buffer (TLB) misses for their CPI stack calculation.

Performance counters are not only used to analyze performance, but are also useful for compiler optimizations through an off-line learning model, as shown in  $[CFA^+07]$ . In the paper from Singh et al. [SBM09], a model derived from performance counters is used to implement a thread scheduler that takes power consumption into consideration. Another paper from F. Bellosa [Bel00] also describes thread scheduling by enriching the thread context with performance counter and known energy values. Having a framework that can reliably trigger performance events can be used for validation and testing such implementations.

Modeling the power consumption based on performance counters is also a possible application. In the papers from Bircher and John [BJ12], Lewis et al. [LGT08] and Isci and Martonosi [IM03], models are developed estimating the power consumption as a function of performance counters dependent on the workload. The work from Contreras and Martonosi [CM05] also build a model based on performance counters but focuses on embedded devices with a specific CPU and memory. Kadayif et al. [KTK<sup>+</sup>01] provide a tool based on performance counters for the UltraSPARC platform which provides energy estimations. They all show that performance counters can be used for power estimations. It is therefore expected that the proposed framework for approximating power consumption by triggering counter events is a viable approach and can help in model validation and test cases for tooling and instrumentation.

In a paper from Zaparanakus et al. [ZJH09], an overview on the accuracy of the measurement infrastructure for multiple CPUs is presented. Weaver et al. [WTM13] for instance identified two major deviations, which can influence counter values. Weaver also researched the overhead of common performance counter implementations and found that the current PAPI interface has large overheads [Wea15]. Despite research in the area of performance counter accuracy, none of the mentioned works treated the accurate generation of counter events.

## 4. Approach

This thesis aims to develop a framework leveraging performance counters that can approximate workloads locally which would usually be driven by external load generators. The approach described in this section shows how the proposed approximation is measured and evaluated.

Before an implementation can be made, first the most relevant performance counters have to be identified. A correlation analysis is made on the reference measurement of the NFV workload. It is the most diverse workload and also stresses the SUT's NICs.

To prove that an approximation is possible, multiple implementations are made with the purpose of triggering events. Each event trigger is then evaluated if it can accurately generate performance counter events, reaching the target value without over or under counting. As counters might be able to introduce side effects on other counters that are implemented, it is necessary to identify them and incorporate these side effects in the framework.

After the most viable implementation for each event trigger is selected, the framework is build and evaluated against the local benchmarks described in Section 2.4. The power consumption of the local workloads is measured under different load levels and the performance counters are recorded. If the framework is able to approximate the local references, it shows that simulating power consumption through performance counters is a reasonable approach.

During all reference and evaluation measurements, performance counters are recorded for evaluation against a linear regression model, based on the preexisting local reference measurements. It is used as a second evaluation step for the framework's approximation performance.

## 4.1. Reference Workloads

This section describes the purpose of the selected workloads. The local workloads introduced in Section 2.4 are used for feasibility while the NFV workload acts as the externally driven application.

### 4.1.1. Local Workloads

To act as reference if workloads can be approximated through performance counters, three locally executable workloads stressing specific parts of a SUT with increasing complexity are selected.

- *Pi worklet*: Simple approximation of  $\pi$ . Mainly stresses the CPU.

- *XMLValidate*: Validates XML file according to a schemata. Stresses both the CPU and memory.

- *SSJ*: A simulation of OLTP, resembling a real world application. This worklet put CPU, memory and caches under load.

These workloads are not dependent to be driven by an external load generator. They therefore do not have I/O heavy operations resulting from network traffic or otherwise. Yet they stress certain aspects of SUT to evaluate the feasibility of the proposed approximation framework. Measurements are performed as described in Section 2.2.1.

### 4.1.2. NFV Workload

The NFV workload, described in more detail in Section 5.2, acts as the externally driven reference workload. As VNFs are stressing the network adapter, which is not used by the local workloads, a VNF is a good example for externally driven workloads. The selected VNF is a DPI firewall inspecting User Datagram Protocol (UDP) packets and checking them for validity.

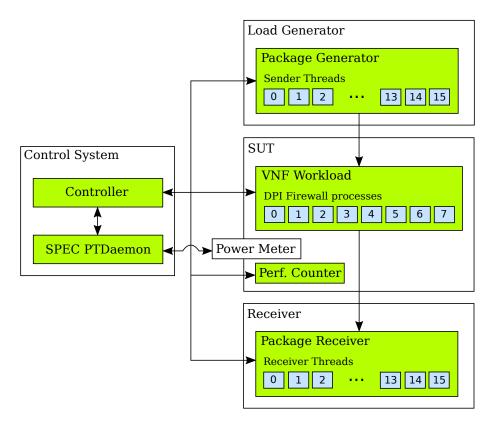

To put the SUT under stress, network traffic needs to be generated. A traffic generator is implemented that produces suitable traffic and is able to saturate the available network connection. The generator must also be able to run at different load levels like the Chauffeur harness for measurements to be comparable. A receiver is installed, to which allowed packets are routed to ensure the VNF is working correctly and can be calibrated.

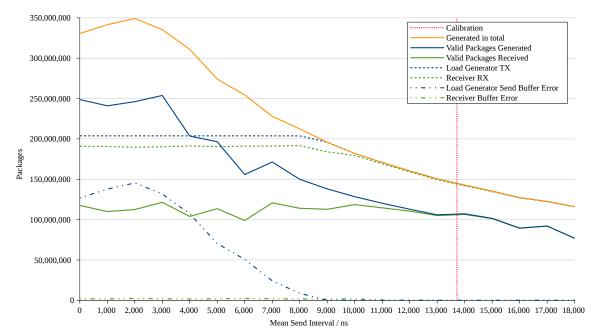

One of the main problems in calibrating the testbed is the non-blocking behavior of the implemented transactions (packets inspected by the DPI). This is inherent to most externally driven workloads as no knowledge about the SUT's current transaction status is available. To perform a reference measurement with actual external traffic, calibrating the VNF deviates from the procedure introduced in Section 2.2.1. The maximum throughput is defined as the number of packets handled by the SUT without dropping packets due to overload. A disadvantage is that the overload is likely to happen because the network bandwidth is saturated instead of the SUT's CPU and memory. Calibration is done via binary search until the threshold of packets dropped is within reasonable bounds or the maximum number of steps is reached. Afterwards measurements are taken in the described manner, recording the following data:

- Valid packets send

- Malicious packets send

- Packets received

- Performance counters

- Power consumption

## 4.2. Workload Approximation

To achieve a workload approximation through performance counters, suitable candidates have to be identified from the available sources, IntelPCM and the OS. The available performance counters are presented and suitable counters are selected. Afterwards the possible influences of side effects when triggering events is described.

20

### 4.2.1. Selection of Available Performance Counters

A wide variety of performance counters are available on modern systems. Not only are counters measured by the CPU itself but also by the OS. To identify and select counters that have an influence on power consumption, the Pearson correlation between counters and the power consumption is calculated for different load levels also used in the evaluation. Ten load levels ranging from 10 % to 100 % in 10 % steps are used. The measurement from which the correlation is calculated is the VNF workload, as the proposed framework should be able to approximate externally driven workloads. A correlation below 0.8 is considered to low for implementation. Feasibility of implementation is considered as well as a second criteria. This is necessary because it might be possible that some performance counters might not be susceptible to manipulation from user space programs and need modifications of the OS to work, which is not within the scope of this thesis. On the other hand, some performance event triggers might be implemented with only minor changes to already selected counters, justifying a lower correlation in certain cases.

Performance counters with values that had a constant value of zero or listing hardware configurations during the measurement are omitted.

#### **CPU** Performance Counters

The correlations are presented in Table 4.1 and descriptions are cited from [Wil]. The C-State (CPU power saving states) residency counters are also omitted. This is due to external tools needed or a CPU specific self-written implementation to send the CPU to a defined C-State. This might not be executable on other hardware other than the SUT's. The QuickPath Interconnect (QPI) and L3 cache occupancy metrics are omitted because they are not measured in the IntelPCM configuration used for this thesis. CPU internal power metrics are omitted because the power consumption is measured externally. Temperature readings are not a part of this thesis.

The EXEC counter is not selected, despite high correlation, as it is dependent on FREQ. IPC's correlation is not deemed sufficient for implementation. FREQ has high correlation but the framework should approximate a workload under real conditions in which the frequency is usually not influenced by user space programs. It is also dependent on ACYC. The same is true for AFREQ. Its high correlation is caused by a nearly constant value as a fraction of the CPU's design frequency. L3MPI and L2MPI are a byproduct of INSTand L3MISS / L2MISS with low correlation. ACYC is well correlated, but not selected for the same reasons as FREQ. The TIME(ticks), PhysIPC and PhysIPC% counters are not selected due to low correlation. INSTnom and INSTnom% are dependent on INSTwhich is selected to be implemented.

Counters implemented that have a high correlation without directly modifying the CPU's configuration are L3MISS, L2MISS, READ, WRITE and INST. Despite lower correlation, L3HITs and L2HITs are selected. If a memory access misses L2, it could either hit or miss L3. It therefore seems reasonable to select L3HIT as L2 misses could directly generate L3 hits or misses if needed. As all other cache related performance counters are selected and the cache's content need to be controlled in a specific manner, L2HIT is therefore selected as well despite moderate correlation.

#### Linux Recorded Performance Counters

The performance counter correlations together with a description, taken from [BBN<sup>+</sup>] and shortened where necessary, are presented in Table 4.2 and 4.3.

For this thesis, *user* is not selected despite a high correlation value. The number of background programs cannot be influenced as the SUT is already running with a minimum

| Perf. counter                   | Correlation | Selected     | Description                                                                 |  |

|---------------------------------|-------------|--------------|-----------------------------------------------------------------------------|--|

| EXEC                            | 0.976       |              | Instructions per nominal CPU cycle ignoring                                 |  |

|                                 |             |              | turbo and power saving modes                                                |  |

| IPC                             | 0.577       |              | Instructions per cycle                                                      |  |

| $\operatorname{FREQ}$           | 0.981       |              | Frequency relative to nominal CPU fre-                                      |  |

|                                 |             |              | quency                                                                      |  |

| AFREQ                           | 0.992       |              | Frequency relative to nominal CPU fre-                                      |  |

|                                 |             |              | quency excluding the time when the CPU is                                   |  |

|                                 | 0.000       | /            | sleeping                                                                    |  |

| L3MISS                          | 0.968       | V            | L3 cache line misses                                                        |  |

| L2MISS                          | 0.983       | V            | L2 cache line misses                                                        |  |

| L3HIT                           | -0.629      | ✓            | L3 cache hits                                                               |  |

| L2HIT                           | 0.727       | $\checkmark$ | L2 cache hits                                                               |  |

| L3MPI                           | 0.478       |              | L3 cache misses per instruction                                             |  |

| L2MPI                           | -0.693      |              | L2 cache misses per instruction                                             |  |

| READ                            | 0.943       | $\checkmark$ | Memory read traffic                                                         |  |

| WRITE                           | 0.969       | $\checkmark$ | Memory write traffic                                                        |  |

| INST                            | 0.976       | $\checkmark$ | Number of instructions retired                                              |  |

| ACYC                            | 0.981       |              | Number of clockticks including turbo and                                    |  |

|                                 | 0.000       |              | power saving modes                                                          |  |

| $\mathrm{TIME}(\mathrm{ticks})$ | -0.203      |              | Number of invariant clockticks invariant to<br>turbo and power saving modes |  |

| PhysIPC                         | 0.582       |              | <i>IPC</i> multiplied by number of threads per core                         |  |

| PhysIPC%                        | 0.576       |              | <i>PhysIPC</i> relative to maximum <i>IPC</i>                               |  |

| INSTnom                         | 0.976       |              | Instructions per nominal cycle multiplied by                                |  |

|                                 | 0.010       |              | number of threads per core                                                  |  |

| INSTnom%                        | 0.976       |              | INST nom relative to maximum IPC                                            |  |

| Table 4.1.: CPU performance coun | ters |

|----------------------------------|------|

|----------------------------------|------|

of software installed and the number of processes created by the test harness is fixed. The *softirq* counter is not selected even with high correlation because software interrupt are handled only after a system call or hardware interrupt [Pro06]. Therefore hardware interrupts are deemed sufficient. Yet it should not be discarded but implemented in the future to possibly improve the proposed framework. The *processes* counter has a good correlation but was not selected as the implementation for context switches (*ctxt*) creates threads which will interfere with this counter. As with the *softirq* counter, it should be kept in mind for further improvements. All other not selected counters correlation is deemed too low to be selected.

Hardware interrupts (irq) and the number of context switches (ctxt) are selected due to their high correlation.

| Perf. counter         | Correlation | Selected     | Description                                                     |

|-----------------------|-------------|--------------|-----------------------------------------------------------------|

| user                  | 0.874       |              | Normal processes executing in user mode                         |

| system                | 0.565       |              | Processes executing in kernel mode                              |

| idle                  | -0.675      |              | Processes currently idling                                      |

| iowait                | -0.322      |              | Waiting for I/O to complete                                     |

| $\operatorname{ctxt}$ | 0.992       | $\checkmark$ | Number of context switches                                      |

| processes             | -0.984      |              | Number of processes and threads created                         |

| procs_running         | 0.685       |              | Number of threads running or ready to run<br>(runnable threads) |

| procs_blocked         | -0.055      |              | Number of processes blocked, waiting for I/O to complete        |

| softirq               | 0.993       |              | Software interrupts serviced since boot time                    |

| irq                   | 0.997       | $\checkmark$ | Number of interrupts serviced since boot time                   |

Table 4.2.: Linux performance counters

The memory performance counters are also read. Yet none of them is selected for implementation. The reasons are low correlation and feasibility of implementation such as *SReclaimable*, which is is part of the in-kernel data structure cache *Slab*. The only two counters not falling into these two categories are *MemFree* with a correlation of 0.975 and *MemAvailable*, with -0.821. Test implementations are made to influence these counters but no noticeable impact could be measured. Further evaluation of these counters for future implementation is therefore necessary but is not within the scope of this thesis.

### 4.2.2. Side Effects of Triggering Performance Events

Triggering performance events to modify the counters can have side effects, especially counters for more abstract events such as context switches. But also counters closer to hardware do have side effects. A read operation on memory for instance could trigger cache misses or hits, depending on the cache lines currently residing in cache. Therefore side effects for each selected performance counters are evaluated by generating a large number of each events individually. The degree to which an event causes side effects on other counters is measured and included in the frameworks configuration.

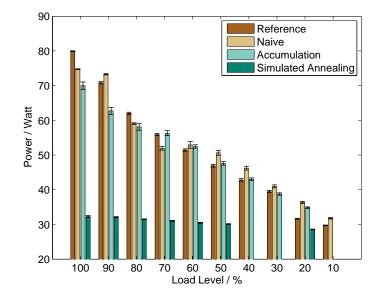

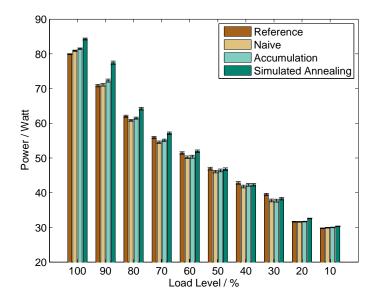

To determine if side effects improve the approximation, two composition mechanisms are implemented for evaluation. First an accumulation method is implemented as shown in Equation 4.1. The accumulated side effects  $s_x$  affecting the event count  $v_x$  are calculated by multiplying the side effects for a single event  $s_i$  with the number of events causing the

| Perf. counter  | Correlation | Description                                                                                                                                                                                                                                                                                                |

|----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MemFree        | 0.975       | The sum of LowFree and HighFree                                                                                                                                                                                                                                                                            |

| MemAvailable   | -0.821      | An estimate of how much memory is available for<br>starting new applications, without swapping. Calcu-<br>lated from <i>MemFree</i> , <i>SReclaimable</i> , the size of the file<br>Least Recently Used (LRU) lists, and the low water-<br>marks in each zone.                                             |

| Buffers        | -0.984      | Relatively temporary storage for raw disk blocks                                                                                                                                                                                                                                                           |

| Cached         | -0.984      | In-memory cache for files read from the disk (the page-<br>cache). Does not include <i>SwapCached</i> .                                                                                                                                                                                                    |

| Active         | -0.984      | Memory that has been used more recently and usually<br>not reclaimed unless absolutely necessary.                                                                                                                                                                                                          |

| Inactive       | -0.950      | Memory which has been less recently used. It is more<br>eligible to be reclaimed for other purposes                                                                                                                                                                                                        |

| Active(anon)   | -0.531      | Not available                                                                                                                                                                                                                                                                                              |

| Active(file)   | -0.984      | Not available                                                                                                                                                                                                                                                                                              |

| Inactive(file) | -0.950      | Not available                                                                                                                                                                                                                                                                                              |

| Dirty          | -0.165      | Memory which is waiting to get written back to the disk                                                                                                                                                                                                                                                    |

| Writeback      | 0.290       | Memory which is actively being written back to the disk                                                                                                                                                                                                                                                    |

| AnonPages      | -0.575      | Non-file backed pages mapped into userspace page ta-<br>bles                                                                                                                                                                                                                                               |

| Mapped         | -0.721      | Files which have been mmaped, such as libraries                                                                                                                                                                                                                                                            |

| Slab           | 0.627       | In-kernel data structure cache                                                                                                                                                                                                                                                                             |

| SReclaimable   | -0.935      | Part of <i>Slab</i> , that might be reclaimed, such as caches                                                                                                                                                                                                                                              |

| SUnreclaim     | 0.714       | Part of <i>Slab</i> , that cannot be reclaimed on memory pressure                                                                                                                                                                                                                                          |

| KernelStack    | 0.587       | Not available                                                                                                                                                                                                                                                                                              |

| PageTables     | -0.043      | Amount of memory dedicated to the lowest level of                                                                                                                                                                                                                                                          |

| 0              |             | page tables                                                                                                                                                                                                                                                                                                |

| Committed_AS   | -0.028      | The amount of memory presently allocated on the system. The committed memory is a sum of all of the memory which has been allocated by processes, even if it has not been "used" by them as of yet. A process which malloc()'s 1 GiB of memory but only touches 300 MiB of it will show up as using 1 GiB. |

Table 4.3.: Linux memory performance counters

effect  $v_i$ . The effects are summed over all event triggers *i*. If the resulting accumulated side effects are lower than  $v_x$ , they are subtracted and set as the new count of events to trigger including side effects  $v_{s,x}$ . In case  $s_x$  is higher than  $v_x$ , the new count is set to zero, triggering no events.

$$s_x = \sum_{i=1}^n s_i \cdot v_i$$

$$v_{s,x} = \begin{cases} v_x - s_x & \text{if } s_x \le v_x \\ 0 & \text{if } s_x > v_x \end{cases}$$

(4.1)

It is likely that the simple aforementioned method is not an optimal solution when balancing side effects and number of events to generate. An analytic solution to this problem might not be feasible to obtain. Therefore simulated annealing is used to find an optimal solution. Simulated annealing is selected as it is less prone to be caught in local maxima or minima like hill climbing. The following description is mainly based on [HJJ03] and adapted to the proposed framework.

In simulated annealing the global minimum solution  $\omega^*$  is searched in the solution space  $\Omega$  with  $\omega^* \in \Omega$ . To find the global minimum, an energy function  $f : \Omega \to \mathbb{R}$  is needed to assess if a solution is closer to the minimum, while the condition  $f(\omega) \ge f(\omega^*)$  must be fulfilled. As energy function, a modified Mean Squared Error (MSE) function as shown in Equation 4.2 is used.  $\hat{\omega}_i$  is the target value for the *i*-th operation,  $\omega_i$  the current value and  $\omega_{s,i}$  the side effects imposed by the current configuration.

$$f(\omega) = \frac{1}{n} \sum_{i=1}^{n} \left(\hat{\omega}_i - \omega_i - \omega_{s,i}\right)^2 \tag{4.2}$$

Each solution  $\omega$  has neighbors defined by a neighborhood function  $N(\omega)$ . A neighbor is a solution that can be reached within a single iteration. A neighboring solution  $\omega' \in N(\omega)$  is calculated by selecting a random operation  $\omega_i$  and incrementing it by one. If a calculated neighbor is accepted based on the acceptance probability in Equation 4.3 with  $t_k$  as the temperature parameter or cooling schedule at iteration k.  $t_k$  is defined such that  $t_k > 0$  for all k and  $\lim_{k \to +\infty} t_k = 0$ .

$$P\{\text{Accept } \omega' \text{ as next solution}\} = \begin{cases} e^{\frac{-\Delta_{\omega,\omega'}}{t_k}} & \text{if } \Delta_{\omega,\omega'} > 0\\ 1 & \text{if } \Delta_{\omega,\omega'} \le 0 \end{cases}$$

(4.3)

If the temperature T is reduced slowly, then simulated annealing can reach a steady state. The probability of the system in state  $\omega$  with the energy  $f(\omega)$  at temperature T follows a Boltzmann distribution. As distance metric  $\Delta_{\omega,\omega'}$ , shown in 4.4, is used.

$$\Delta_{\omega,\omega'} = f\left(\omega'\right) - f\left(\omega\right) \tag{4.4}$$

First the initial solution is selected, the temperature change counter is set k = 0. Afterwards the temperature parameter  $t_k$  and the initial temperature  $T = t_0 \ge 0$  are selected. Finally before the algorithm can start,  $M_k$  is set which defines the number of iterations at each temperature. Then the algorithm is ready and can be started. It repeats the following steps until the stopping criterion is met by either finding the minimum energy or a predefined number of iteration steps were executed.

25

- 1. Set repetition counter m = 0

- a) Generate a solution  $\omega' \in N(\omega)$

- b) Calculate  $\Delta_{\omega,\omega'}$

- c)  $\omega \leftarrow \omega'$  with probability from 4.3

- d)  $m \leftarrow m + 1$

- e) If not  $m = M_k$ , then go o a)

- 2.  $k \leftarrow k+1$

- 3. If stopping criterion is not met, then go to 1.

### 4.3. Regression Model

As stated earlier, a linear regression model based on measurements from the local reference workloads Pi, XMLValidate and SSJ is created as as a second evaluation method. If the model is able to predict the power consumption generated by the framework, it shows that performance counters are able to approximate workloads independent of external appliances. If the prediction for the NFV workload is false, but correct for local workloads, it gives an indication that hardware used by externally driven workloads can significantly influence the approximation when trying to simulate them. In case the local and NFV workloads are incorrect, it shows that the used modeling approach is not sufficient for approximating power consumption through the selected performance counters if the measurements show a working approximation.

The model is generated using multiple linear regression. The following section is based on [FKLM13]. The power consumption y is modeled through the input parameters, the performance counters,  $x_1, \ldots, x_k$ . y is therefore modeled as the conditional expected value  $E(y|x_1, \ldots, x_k)$  and can be written in a general form as shown in Equation 4.5.

$$y = \beta_0 + \beta_1 x_1 + \dots + \beta_k x_k + \epsilon \tag{4.5}$$

The model parameters  $\beta_0, \beta_1, \ldots, \beta_k$  need to be estimated from the reference measurements. The first parameter  $\beta_0$  is the intercept. Both x and  $\beta$  can be written in vector form, including the intercept. So we obtain  $\boldsymbol{\beta} = (\beta_0, \beta_1, \ldots, \beta_k)$  and  $\boldsymbol{x} = (1, x_1, \ldots, x_k)'$ . The Equation 4.5 can now be written as  $y = \boldsymbol{x}' \boldsymbol{\beta} + \epsilon$ .

| Performance counter                | Estimated coefficient $\beta$ | Standard Error         |

|------------------------------------|-------------------------------|------------------------|

| Intercept                          | 23.214                        | 1.1483                 |

| L3 misses                          | $1.2528 \cdot 10^{-4}$        | $2.2907 \cdot 10^{-5}$ |

| L3 hits                            | $-7.878 \cdot 10^{-5}$        | $1.4998 \cdot 10^{-5}$ |

| Bytes read from memory controller  | $-5.8589 \cdot 10^{-8}$       | $9.7646 \cdot 10^{-9}$ |

| Bytes written to memory controller | $-3.8536 \cdot 10^{-8}$       | $2.236\cdot 10^{-8}$   |

| Instructions retired               | $1.184 \cdot 10^{-8}$         | $2.744 \cdot 10^{-9}$  |

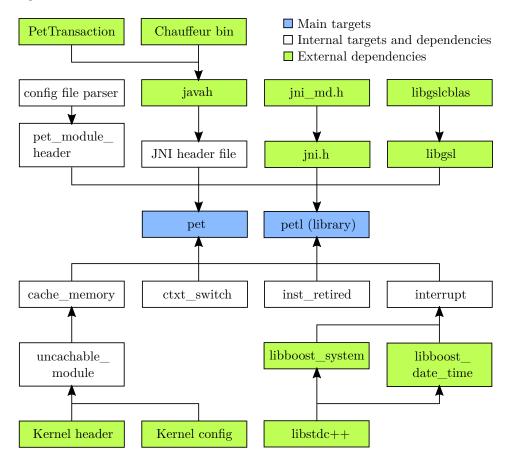

| Interrupts                         | $3.659\cdot10^{-3}$           | $1.3766 \cdot 10^{-3}$ |